DAC is where both sides of the design equation come together for discussion and learning. This is what makes attending DAC discussion panels so interesting; you are going to hear from providers of tools, methodologies and IP as well as those who need to use them to deliver working solutions. There are few places where the interplay… Read More

Electronic Design Automation

Accelerating the PCB Design-Analysis Optimization Loop

With the increasing complexity and diversity of the mechanical constraints and electrical requirements in electronic product development, printed circuit board designers are faced with a number of difficult challenges:

- generating accurate (S-parameter) simulation models for critical interface elements of the design

AMS Experts Share IC Design Stories at #55DAC

At #55DAC in SFO the first day is always the busiest on the exhibit floor, so Monday by lunch time I was hungry and took a short walk to the Marriott hotel nearby to listen to AMS experts from several companies talk about their EDA tool use, hosted by Synopsys:

- Samsung

- Toshiba Memory Corp.

- NVIDIA

- Seagate

- Numem

- Esperanto

Verification Importance in Academia

“Testing can only prove the presence of bugs, not their absence,” stated the famous computer scientist Edsger Dijkstra. That notion rings true to the many college participants of the Hack@DAC competition offered during DAC 2018 in San Francisco. The goal of this competition is to develop tools and methods for identifying security… Read More

Webinar: Differential Energy Analysis for Improved Performance/Watt in Mobile GPU

May want to listen up; Qualcomm are going to be sharing how they do this. There is a constant battle in designing for low power; you don’t accurately know what the power consumption is going to be until you build it, but by the time you’ve built it, it’s too late to change the design. So you have to find methods to estimate power early on,… Read More

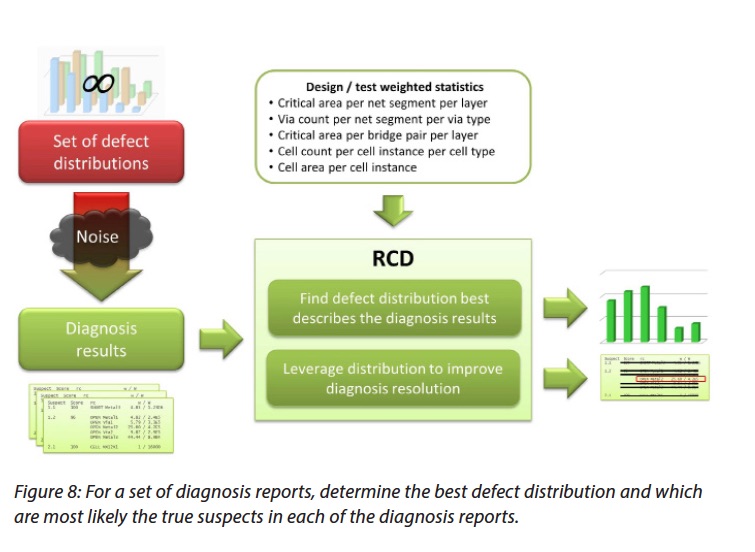

Machine Learning Meets Scan Diagnosis for Improved Yield Analysis

Naturally, chips that fail test are a curse, however with the advent of Scan Logic Diagnosis these failures can become a blessing in disguise. Through this technique information gleaned from multiple tester runs can help pin down the locations of defects. Initially tools that did Scan Logic Diagnosis relied on the netlist to filter… Read More

Daniel’s #55DAC Trip Report

Another year, another DAC, and last month it was #55DAC in SFO and the first thing that I noticed was that the event was no longer located in the traditional North or South Halls, rather we were in the smaller, Moscone West on two floors, almost like a 3D FinFET. Checkin to get my badge was highly automated and oh so fast, well done.… Read More

1-on-1 with Anirudh Devgan, President, Cadence

At the Design Automation Conference, no one is busier than an EDA company executive — conference panels, product launch briefings, customer meetings, and corporate dinners all place considerable demands on their time. I was fortunate enough to be able to meet with Anirudh Devgan, President of Cadence, at the recent DAC55 in San… Read More

Low Cost Power NB-IoT Solution? Fusion F1 DSP based Modem!

Supporting NB-IoT requires low cost (optimized silicon footprint) and ultra-low power solution to cope with IoT device requirement. Cadence Fusion F1 DSP IP has been integrated in modem IC by two new customers, Xinyi and Rafael, gaining traction in NB-IoT market. These design-win builds on previous momentum: software GPS solution… Read More

Cadence Selected to Support Major DARPA Program

When DARPA plans programs, they’re known for going big – really big. Which is what they are doing again with their Electronics Resurgence Initiative (ERI). Abstracting from their intro, this is a program “to ensure far-reaching improvements in electronics performance well beyond the limits of traditional scaling”. This isn’t… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center