Another year, another DAC, and last month it was #55DAC in SFO and the first thing that I noticed was that the event was no longer located in the traditional North or South Halls, rather we were in the smaller, Moscone West on two floors, almost like a 3D FinFET. Checkin to get my badge was highly automated and oh so fast, well done.

EDA vendors with huge signage included Mentor (a Siemens business) and Synopsys. Sunday night includes live music, finger food, drinks and plenty of networking with old friends and rivals.

Rich Valera from Needham bravely tried to speak above the loud crowd to remind us that EDA and IP companies have outperformed the NASAQ composite during the past 10 years by a factor of 2X, so investors take note. I looked for the usual C-level executives from Mentor, Cadence and Synopsys, but alas, they were no-shows this year. During the week, yes, you could spot them walking through the exhibit area and at other events.

On Monday morning there were long lines at the registration counter, but they did move quite briskly, not like Disney Land.

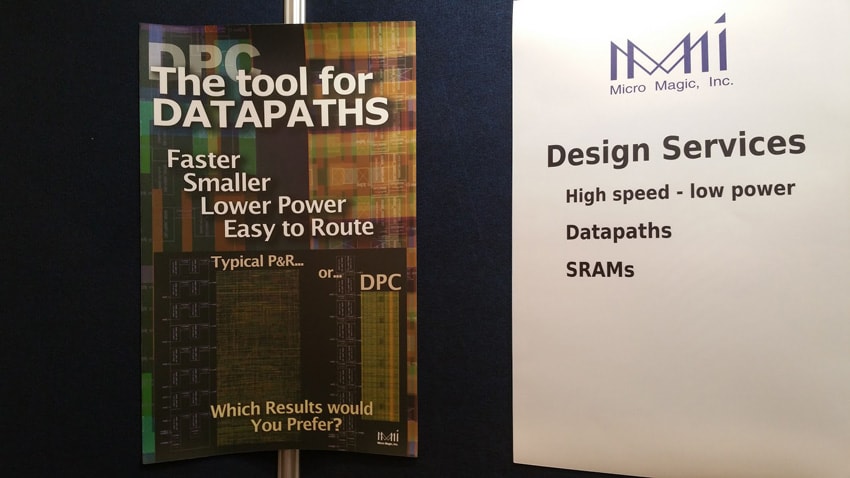

My first vendor stop in the exhibits was MicroMagic to see my former Silicon Compiler co-worker Katherine Hayes. They have a unique Datapath Compiler tool that helps designers get smaller area and higher performance than using standard cells with traditional place and route tools. They offer both tools and design services, although you can expect to see them focusing more on the design services side in 2018.

My social media savvy contact Anupam Bakshi is the founder and CEO of Agnisys, and they offer IDesignSpec to enable IP, SoC and FPGA teams to standardize on register specifications and then automatically generate Verilog, VHDL, UVM, C headers, Word, Excel and PDF format documents from it.

Lunch time on Monday was spent across the street from Moscone at the Marriott where Synopsys hosted AMS experts (Samsung, Toshiba Memory Corp, NVIDIA, Seagate, Numem, Esperantro) to talk about their IC design challenges while using Custom Compiler and other tools. There’s a separate blog on that event here.

An IP vendor named Moortec had so many staff that they couldn’t all fit into their booth space, and I attended their presentation at the TSMC booth instead. Their IP provides on-chip monitoring of Process, Voltage and Temperature (PVT). Lots of tier one clients use their specialized IP instead of creating something custom.

One of my favorite EDA vendors from Munich is privately held Concept Engineering, and they have visualization software at the transistor, gate and RTL levels. They even sell their software to other EDA companies to bundle inside of bigger tools.

Students from Universities are encouraged to write papers and then present their ideas in the aisles in poster slides, it’s quite a success.

To cap off Monday evening I was invited to the classy dinner event hosted by Mentor, and our entertainment was uniquely quiet for a change, and I got to meet Tony Hemmelgarn of Siemens PL, the group that Mentor reports into. I congratulated Tony on how smooth the Mentor acquisition was going in terms of growing headcount and employee morale, something rare in the world of EDA mergers.

On Tuesday I met up with Ramy Iskander of Intento Design, and you can read about this new kind of Analog EDA company in my June blog. STMicroelectronics is their first customer and they used the tools on FD-SOI designs.

From the IP side I met with Meredith from CAST Inc, and this was their 24th appearance at DAC. Their IP is used in many segments like automotive ethernet and GZIP lossless compression for high throughput.

EDA in the cloud was another emerging theme, so there was a Cloud Alley setup in the exhibit area, visitor looked interested with lots of traffic.

Coolest looking super car was for sure the McLaren P1 on display at the ICManagebooth. Having a car on display is the hallmark of this vendor, and it draws people into the booth like magic. One of their themes this year was, “Run your existing workflows in the cloud.”

Silvaco and other IP vendors hosted a Tuesday night networking event nearby, and it was a smashing success without smashing your eardrums. I even managed to con my way into the event, even without an official wristband.

Wednesday was my last day at DAC and a favorite startup called Scientific Analog showed off their XMODEL tool to help analog designers automatically create SystemVerilog models for faster simulation.

My final free lunch at DAC was sponsored by Cadence with guests talking about, “Meeting Analog Reliability Challenges”. Their panelists were: Elyse Rosenbaum – Professor at the U of Illinois, Mark Porter – Medtronics, Saverio Fazzari – Booze, Allen and Hamilton, L. Balasubramanian – TI, Vinod Kariat – Cadence. Stay tuned for a separate blog on that.

On a final note, we learned at DAC that Synopsys will NOT be attending #56DAC in Las Vegas, probably because they are already number one in EDA revenue and their absence doesn’t tarnish their reputation that much.

Share this post via:

Solving the EDA tool fragmentation crisis