Check this webinar out – Mediatek will share a novel approach to early IR drop estimation. Competition in system design has become even more intense because potential markets are huge and there are more players with deep pockets chasing those markets. Wherever you are in those value chains, you want to shift everything left to accelerate… Read More

Electronic Design Automation

Easing Your Way into Portable Stimulus

The Portable Stimulus Standard (PSS) was officially released at DAC this year. While it will no doubt continue to evolve, for those who were waiting on the sidelines, it is officially safe to start testing the water. In fact it’s probably been pretty safe for a while; vendors have had solutions out for some time and each is happy to … Read More

Fuzzing on Automotive Security

The ECU. That was the service department prognosis on the root cause of thealways-on air bag safety light on my immaculate car. Ten years ago the cost for its replacement with after market part was at par with getting a new iPhone 8. Today, we could get four units for the same price and according to data from several research companies,… Read More

DesignWare IP as AI Building Blocks

AI is disruptive and transformative to many status quos. Its manifestation can be increasingly seen in many business transactions and various aspects of our lives. While machine learning (ML) and deep learning (DL) have acted as its catalysts on the software side, GPU and now ML/DL accelerators are spawning across the hardware… Read More

Affordable EDA Tools for IoT Designs, Guess which Vendor

I just had to drive my car 7 miles from Tualatin, Oregon to visit with an EDA veteran who has played a lot of diverse roles in his career, including: IC Mask Designer, Layout Manager, Account Manager, Business Development, Director, Foundry Relations Director. His name is John Stabenow, with Mentor, a Siemens Business, and we met… Read More

A Fresh Idea in Differential Energy Analysis

When I posted earlier on Qualcomm presenting with ANSYS on differential energy analysis, I assumed this was just the usual story on RTL power estimation being more accurate for relative estimation between different implementations. I sold them short. This turned out to be a much more interesting methodology for optimizing total… Read More

Accelerating Design and Manufacturing at the 25th Annual IEEE Electronic Design Process Symposium

25th annual IEEE Electronic Design Process Symposium

Accelerating Design and Manufacturing

September 13 & 14, 2018, SEMI, 673 S. Milpitas Blvd, Milpitas, CA 95035

This year marks a milestone in EDPS’s history as it turns 25. The event will be held at SEMI’s new headquarter facility and will provide a forum for EDA, foundry … Read More

IP Management Using both Git and Methodics

I use Quicken to manage my business and personal finances because it saves me so much time by downloading all of my transactions from Chase for credit card, Amazon for credit card, Wells Fargo for banking and Schwab for IRA. Likewise, for IP management in SoC design you want an app like Quicken that plays well with other tools that you… Read More

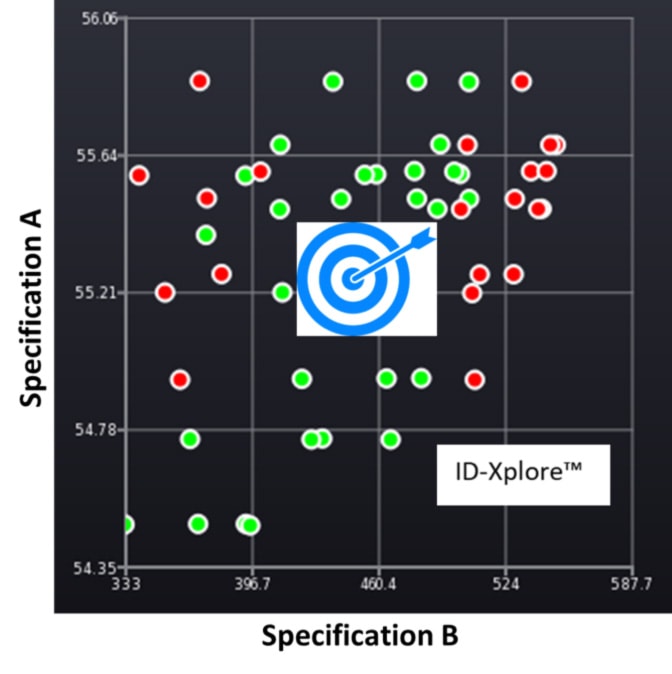

Analog IC design across PVT conditions, something new

Transistor-level design for full-custom and analog circuits has long been a way for IC design companies to get the absolute best performance out of silicon and keep ahead of the competition. One challenge to circuit designers is meeting all of the specs across all Process, Voltage and Temperature (PVT) corners, so that silicon… Read More

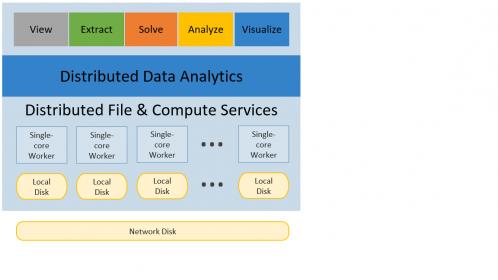

Analytics and Visualization for Big Data Chip Analysis

Designers require comprehensive logical, physical, and electrical models to interpret the results of full-chip power noise and electromigration analysis flows, and subsequently deduce the appropriate design updates to address any analysis issues. These models include: LEF, DEF, Liberty library models (including detailed… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center