There’s a familiar saying that you can’t improve what you can’t measure. Taking that one step further, the more improvement you want, the more accurately you have to measure. This become pretty important when you’re building huge designs in advanced technologies. Margins are a lot tighter all round and use-cases are massively… Read More

Electronic Design Automation

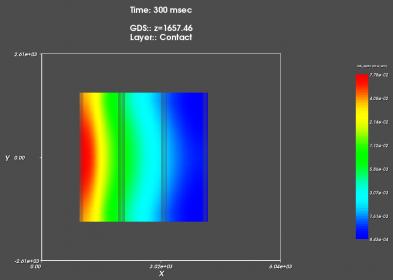

Coupled Electro-thermal Analysis Essential for PowerMOS Design

Power device designers know that when they see a deceptively simple pair of PowerMOS device symbols in the output stage of a power converter circuit schematic, they are actually looking at a massively complex network of silicon and metal interconnect. The corresponding physical devices can have a total device W on the order of … Read More

Emulation from In Circuit to In Virtual

At a superficial level, emulation in the hardware design world is just a way to run a simulation faster. The design to be tested runs on the emulator, connected to whatever test mechanisms you desire, and the whole setup can run many orders of magnitude faster than it could if the design was running inside a software simulator. And … Read More

Why Did Ambiq Micro Select HiFi-5 DSP IP for Next Generation MCU?

Ambiq Micro has built a family of voice processing MCU dedicated to battery powered, energy sensitive systems, supporting mobile application like wearable. The company is facing two strong challenges: support computationally intensive processing (NN-based far field) and speech recognition algorithms, while offering … Read More

The Changing Face of IP Management

Aristotle once said “The whole is greater than the sum of its parts”. The notion of synergism echoes the importance of leveraging design IPs to the maximum extent with the rest of the system under development, in order to ensure a successful SoC design outcome in a shorter development cycle.

SoC design cost and entry point

For over… Read More

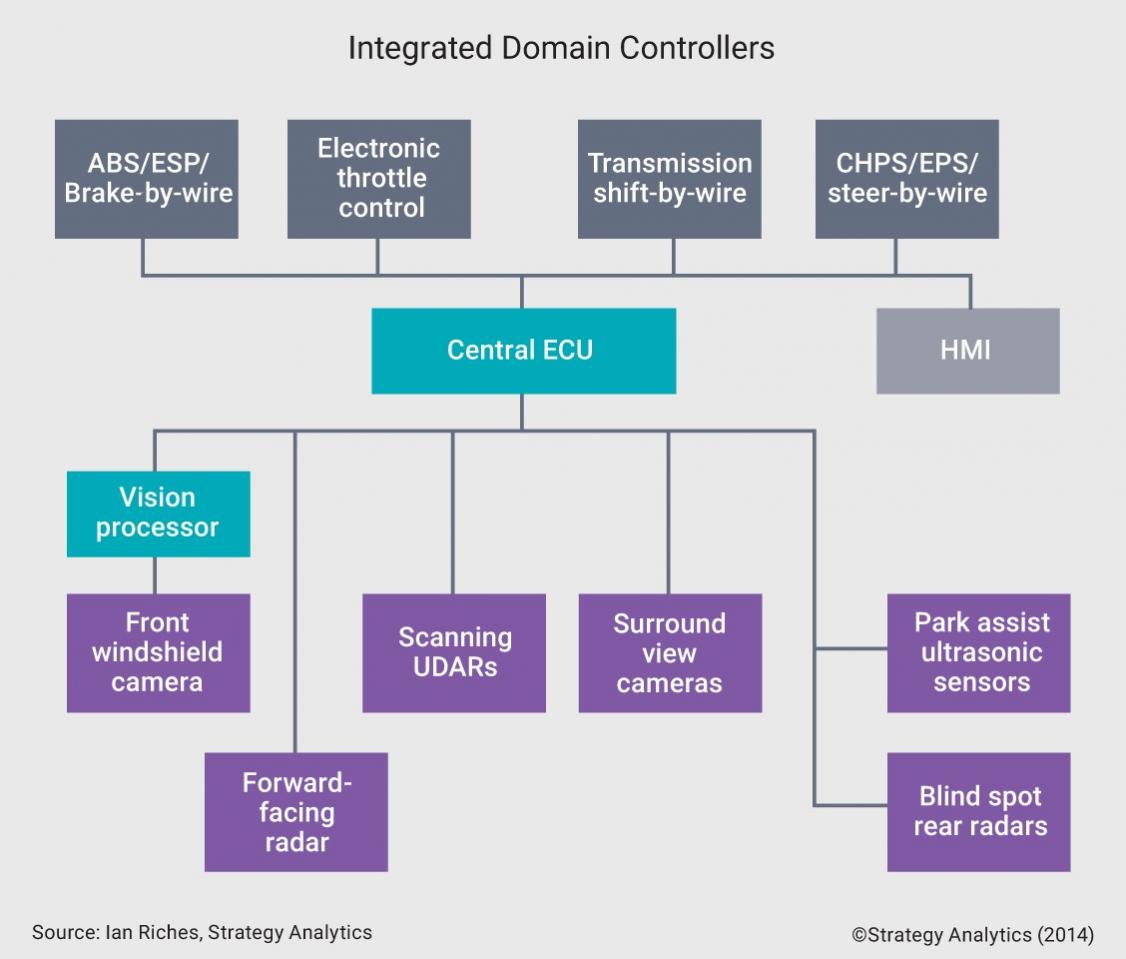

Designing Integrated ADAS Domain Controller SoCs with ISO 26262 Certified IP

As new automotive Advanced Driver Assistance System (ADAS) based product releases intensifies while a more stringent set of safety requirements are mandated, it is not surprising that subsystem and electronic suppliers are looking for pre-designed and ISO 26262 certified IP that can address both imperatives of schedule and… Read More

Mentor’s Busy ITC and Major Test Product Updates

In conjunction with the 2018 International Test Conference, Mentor has several interesting test announcements. They also have a busy round of technical activities, including a number of technical papers, presentations, tutorials and a poster from a major customer about using Mentor. I’d like to touch on the two product related… Read More

Parasitic Extraction for Advanced Node and 3D-IC Designs

Technology scaling has made positive impacts on device performance, while creating challenges on the interconnects and the fidelity of its manufactured shapes. The process dimension scaling has significantly increased metal and via resistance for advanced nodes 7nm and onward, as shown in figures 1a,1b. Similar to a fancy… Read More

Solving and Simulating in the New Virtuoso RF Solution

Cadence has done a good job of keeping up with the needs of analog RF designs. Of course, the term RF used to be reserved for a thin slice of designs that were used specifically in RF applications. Now, it covers things like SerDes for networking chips that have to operate in the gigahertz range. Add that to the trend of combining RF and… Read More

IBIS-AMI Model Generation Simplified

The increasing demand for data communication throughput between system components has driven the requirement for faster SerDes IP data rates. The complexity of the transmit (Tx) and receive (Rx) signal conditioning functions has correspondingly evolved. As a result, the simulation methodology for SerDes electrical interface… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center