You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 140

[name] => Breker Verification Systems

[slug] => breker-verification-systems

[term_group] => 0

[term_taxonomy_id] => 140

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 28

[filter] => raw

[cat_ID] => 140

[category_count] => 28

[category_description] =>

[cat_name] => Breker Verification Systems

[category_nicename] => breker-verification-systems

[category_parent] => 157

[is_post] =>

)

WP_Term Object

(

[term_id] => 140

[name] => Breker Verification Systems

[slug] => breker-verification-systems

[term_group] => 0

[term_taxonomy_id] => 140

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 28

[filter] => raw

[cat_ID] => 140

[category_count] => 28

[category_description] =>

[cat_name] => Breker Verification Systems

[category_nicename] => breker-verification-systems

[category_parent] => 157

[is_post] =>

)

RISC-V is obviously making progress. Independent of licensee signups and new technical offerings, the simple fact that Arm is responding – in fundamental changes to their licensing model and in allowing custom user extensions to the instruction set – is proof enough that they see a real competitive threat from RISC-V.

Which all… Read More

Breker has been in the system test synthesis game for 12 years, starting long before there was a PSS standard. Which means they probably have this figured out better than most, quite simply because they’ve seen it all and done it all. Breker is heavily involved in and aligned with the standard of course but it shouldn’t be surprising… Read More

If you are interested in gaining a deeper understanding of the many ways you can leverage the Universal Verification Methodology (UVM), Breker Verification Systems has gone to a lot of effort to put that information at your fingertips.

A technical subcommittee of Accellera voted to establish the UVM in December 2009. UVM was based… Read More

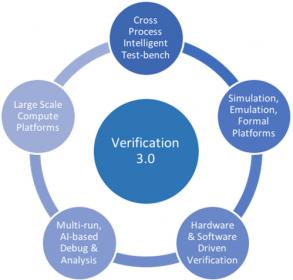

I’ve been following the evolution of the verification space for a very long time including several stints consulting to formal verification companies. It has always been interesting to me to see how so many diverse verification techniques emerge and been used, but without much unification of the approaches. With the emergence… Read More

When PSS comes up, a lot of mainstream verification engineers are apt to get nervous. They worry that just as they’re starting to get the hang of UVM, the ivory tower types are changing the rules of dynamic verification again and that they’ll have to reboot all that hard-won UVM learning to a new language. The PSS community and tool … Read More

Last week I attended the first Verification 3.0 Innovation Summit held at Levi’s Stadium in Santa Clara along with about 90 other interested engineers and former engineers (meaning marketing and sales people, like me). There was a great vibe and feel to the event as it exuded an energy level that I have not felt at an EDA event in years.… Read More

Breker Verification Systems solves challenges across the functional verification process for large, complex semiconductors. This includes streamlining UVM-based testbenches for IP verification, synchronizing software and hardware tests for large system-on-chips (SoCs), and simplifying test sets for hardware emulation… Read More