For observers of EDA markets there is an easily overlooked opportunity for new growth. Today around 50% of EDA revenues come from systems rather than semiconductor companies, from datacenters to automotive, aerospace, energy, and others. In most of these industries total system design depends as much on mechanical and other… Read More

Artificial Intelligence

A Rare Offer from The SHD Group – A Complimentary Look at the RISC-V Market

The web is a wonderful place to find information on almost any topic. While top-level information is easy to find, a deep dive often requires the services of a market research firm. These organizations specialize in “going deep” on many technology topics, offering insights not available with a Google search. And these services… Read More

2023 Retrospective. Innovation in Verification

As usual in January we start with a look back at the papers we reviewed last year. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue our series on research ideas. As always, feedback welcome. We’re planning on starting a live series… Read More

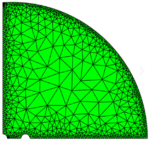

Blending Finite Element Methods and ML

Finite element methods for analysis crop up in many domains in electronic system design: mechanical stress analysis in multi-die systems, thermal analysis as a counterpart to both cooling and stress analysis (eg warping) and electromagnetic compliance analysis. (Computational fluid dynamics – CFD – is a different beast which… Read More

Transformative Year for Sondrel

This is our third year working with Sondrel and it has been a great experience. I have always been fascinated with the ASIC business and put a full chapter about it in our first book “Fabless: The Transformation of the Semiconductor industry.” Companies like Sondrel enabled our move to the fabless model and now they … Read More

CES 2024

CES 2024 is being held this week in Las Vegas, Nevada with an estimated 130,000 attendees and over 4,000 exhibitors. CES (previously Consumer Electronics Show) has been held in Las Vegas every year since 1978, except for 2021 due to COVID-19. This was my ninth CES representing Semiconductor Intelligence, with the first in 2012.… Read More

Synopsys Geared for Next Era’s Opportunity and Growth

As semiconductor industry folks know, Synopsys is a behemoth of a company. At $5.84B in FY2023 revenue (FY Nov-Oct), approximately 20,000 employees and a market cap of about $74B, it leads the silicon-to-systems design solutions space within the industry. From humble beginnings in 1986 as a disruptive startup, the company has… Read More

Navigating the AI Horizon: Trends and Challenges in 2024

Stepping into the year 2024, the landscape of artificial intelligence (AI) continues to evolve at an unprecedented pace, presenting both exciting opportunities and formidable challenges. In this era of technological advancement, we find ourselves at the intersection of innovation and responsibility, where emerging trends

Fail-Safe Electronics For Automotive

The automotive industry is on the brink of a revolutionary transformation, where predictive maintenance and monitoring are taking center stage. In a recent webinar panel session, industry experts delved into the challenges, current approaches, and future innovations surrounding the guarantee and extension of mission profiles.… Read More

Reasoning and Planning as the Next Big Thing in AI

When I search for ‘what is the next big thing in AI?’ I find a variety of suggestions around refining and better productizing what we already know. Very understandable for any venture aiming to monetize innovation in the near term, but I am more interested in where AI can move outside the box, to solve problems well outside the purview… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era