Some of the world’s most complex Systems-on-Chip (SoCs) are being developed for automotive applications. These SoCs have heterogeneous architectures with a variety of processors and accelerators that do real-time image processing for assisted and autonomous driving applications. The Bosch Visiontec team, in Sophia Antipolis, France develops these state-of-the-art SoCs and they recently co-authored a white paper with Mentor, a Siemens Business, that details how they have leveraged high-level synthesis to design these complex ICs.

Some of the world’s most complex Systems-on-Chip (SoCs) are being developed for automotive applications. These SoCs have heterogeneous architectures with a variety of processors and accelerators that do real-time image processing for assisted and autonomous driving applications. The Bosch Visiontec team, in Sophia Antipolis, France develops these state-of-the-art SoCs and they recently co-authored a white paper with Mentor, a Siemens Business, that details how they have leveraged high-level synthesis to design these complex ICs.

Traditional SoC design flows start with designers modeling at the system level in MATLAB or languages like System-C or C++. Once the functional trade-offs have been made, designers implement the design architectures using Register Transfer Language (RTL) code which is used for logic synthesis, placement and routing. In the case of autonomous vehicle applications, the algorithms to do image recognition are mathematically intense and the Bosch team found themselves facing very aggressive design schedules. With autonomous and assisted vehicles being such a new area, Bosch also found that their design specifications were continually changing. With that in mind, the team quickly decided that hand-coding RTL was not going to be a viable option. They needed a way to respond in a nimble fashion to design specification changes while being able to rapidly iterate their RTL design.

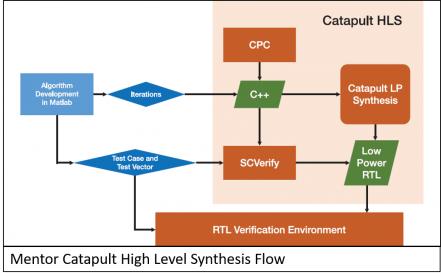

Bosh partnered with Mentor to implement a design flow that used Mentor’s Catapult High Level Synthesis (HLS) and PowerPro platforms. The team chose to implement their designs using a synthesis friendly subset of ANSI C++ and to then use the Catapult flow to synthesize and optimize their design blocks. Using C++ allowed the Bosch team to stay at a higher level of abstraction while also using parameterized functions to avoid writing the same functions multiple times for different designs.

Catapult’s ability to rapidly synthesize RTL code greatly reduced the time to iterate design blocks as micro-architecture constraints changed. Instead of re-coding RTL by hand, the design team was able to simply change the synthesis constraints and have Catapult re-synthesize new RTL code. A good example of this was when one spec change caused the throughput requirement to go from 5 to 20 clock cycles. In this case, Catapult took advantage of the relaxed throughput requirement and re-optimized the RTL to make use of more resource sharing, resulting in an overall area reduction for the design.

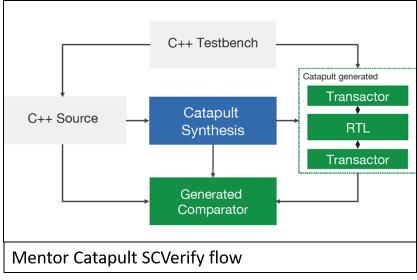

A slick feature of the Catapult-HLS flow is that Catapult can automatically generate the infrastructure for verifying the functionality of the HLS-generated RTL against the original C++ source code. When doing this, Catapult re-uses the original C++ simulation test benches. Mentor calls this their SCVerify flow. When Catapult compiles the C++ design files, it generates scripts that drive the simulator environment for debugging and verifying the design. This saves the team a considerable amount of work and time as they don’t have to manually write a RTL test bench each time the design specifications change.

A slick feature of the Catapult-HLS flow is that Catapult can automatically generate the infrastructure for verifying the functionality of the HLS-generated RTL against the original C++ source code. When doing this, Catapult re-uses the original C++ simulation test benches. Mentor calls this their SCVerify flow. When Catapult compiles the C++ design files, it generates scripts that drive the simulator environment for debugging and verifying the design. This saves the team a considerable amount of work and time as they don’t have to manually write a RTL test bench each time the design specifications change.

Another key advantage to using Catapult came about after Bosch synthesized their generated RTL to gate logic. A design-for-test (DFT) tool was used to analyze the resulting gate logic and it was found that their design had a 95% test coverage score. For safety sensitive automotive applications, this needs to be 99% or higher. Upon seeing their score, the design team went back to the RTL level and made use of Catapult’s LOGIC_OPT directives and found they could further increase the DFT coverage to 97%. Next the design team made use of Catapult’s Optimized Reusable Entities (CCOREs) to increase the clock overhead which allowed them to add more test points, enabling them to meet their 99% goal. These changes were later backed out as there was a specification change that increased the clock overhead but the initial worked enabled them to prove that they could in fact meet the testability requirements as desired.

In addition to HLS, Catapult also gave the Bosch team the ability to do “property checking” on their design. This included checks for uninitialized memory reads (UMRs), divide-by-zero (DBZs), array bound read errors (ABRs) array bound write errors (ABWs), incomplete case statements (CAS) and illegal shift errors (ISEs). Catapult also formally proves designer-provided custom assertions and cover points that are used to complement dynamic simulations and to provide further verification of the C++ models. In Bosch’s case, Captapult’s property checking capabilities enabled them to find and fix hundreds of uninitialized memory read problems that were not possible to detect in their C simulations.

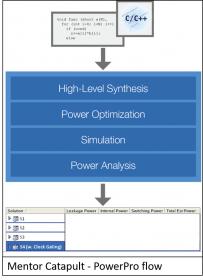

Lastly, the Bosch team also made use of Catapult’s low-power flow that integrates high-level synthesis with Mentor’s PowerPro technology. With this flow, Catapult runs supplementary optimizations to control power consumption by using deep sequential analysis of the RTL for power estimation and optimization. PowerPro uses stability and observability clock gating to generate a power-optimized circuit with minimal user guidance. To do this it uses the same test bench as used in the SCVerify flow to capture switching activities. Additionally, Catapult has built-in formal verification technology that is used to ensure that the power-optimized RTL remains equivalent to the original design intent. By using this flow, Bosch was able to reduce their power consumption by 19% on one chip and 33% on a second chip.

Lastly, the Bosch team also made use of Catapult’s low-power flow that integrates high-level synthesis with Mentor’s PowerPro technology. With this flow, Catapult runs supplementary optimizations to control power consumption by using deep sequential analysis of the RTL for power estimation and optimization. PowerPro uses stability and observability clock gating to generate a power-optimized circuit with minimal user guidance. To do this it uses the same test bench as used in the SCVerify flow to capture switching activities. Additionally, Catapult has built-in formal verification technology that is used to ensure that the power-optimized RTL remains equivalent to the original design intent. By using this flow, Bosch was able to reduce their power consumption by 19% on one chip and 33% on a second chip.

In summary, the Bosch team found that by using the Catapult flow, they were able to complete several complex designs in a very short seven months cycle even though their specifications were evolving over the entire design cycle. They were also able to produce higher quality designs through continuous refinement and as a result they have now fully switched over their design methodology to using the Catapult High-Level Synthesis flow. Kudos to Mentor for taking design synthesis to the next level!

See Also:

Full white paper by Bosch Visiontec and Mentor

Mentor Catapult product page

Comments

There are no comments yet.

You must register or log in to view/post comments.