For about a decade I am looking forward to seeing more of system level design and verification including high level synthesis (HLS), virtual prototyping, and system modeling etc. to come in the main stream of SoC design. Although the progress has been slow, I see it accelerating as more and more tools address the typical pain points… Read More

Author: Pawan Fangaria

Complete SoC Debugging & Integration in a Single Cockpit

These days it’s common to expect large digital designs, analog blocks, custom IPs, glue logic, interfaces and interconnects all developed separately, perhaps by different vendors / teams, but integrated together in a single environment forming an SoC. The SoC can have multiple clock domains and can work in multiple modes of … Read More

Can Android1 Lead the Way for Google in New Smartphone Market?

I had been wanting to write about it since Google’sbig bang announcement of Android1 in India in Sep this year and their associated strategy to capture some of the large pockets of Smartphone market within a matured or declining cell phone market and maturing overall market of Smartphone. Since I wrote my last article hereon maturation… Read More

Look who is Leading the World Semiconductor Business

A couple of days ago I was reading a news article which said how long the world economy will be dependent on a single engine to drive it; obviously that single engine is USA. If we consider the overall economy, definitely USA is driving it, and semiconductor is a large part of it. The semiconductor is driving electronics and that is attracting… Read More

In-Design DFM Signoff for 14nm FinFET Designs

While FinFET yield controversy is going on, I see a lot being done to improve that yield by various means. One prime trend today, it must be, it’s worthwhile, is to pull up various signoffs as early as possible during the design cycle. And DFM signoff is a must with respect to yield of fabrication. This reminds me about my patents filed… Read More

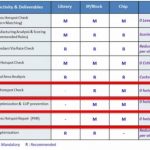

Improve Test Robustness & Coverage Early in Design

In a semiconductor design, keeping the design testable with high test coverage has always been a requirement. However with shrinking technology nodes and large, dense SoC designs and complex logic structures, while it has become mandatory to reach close to 100% test coverage, it’s extremely difficult to cope with the explosion… Read More

Noise & Reliability of FinFET Designs – Success Stories!

I think by now there has been good level of discussion on FinFET technology at sub-20 nm process nodes and this is an answer to ultra dense, high performance, low power, and billion+ gate SoC designs within the same area. However, it comes with some of the key challenges with respect to power, noise and reliability of the design. A FinFET… Read More

Designing Hardware with C++ and its Advantages

Very recently, I was seeing intense discussions on the need for agile hardware development just like agile software and ideas were being sought from experts as well as individuals. While in software world it has already evolved, in hardware world it’s yet to see the shift in paradigm. My point is that the end goal of agile hardware… Read More

ANSYS Electronics Simulation Expo – A View from Industry

As we are seeing more and more automation in most of our activities, not only through software but also smart electronics (at cutting-edge technologies) equipped with processors, micro-controllers, sensors and so on which make a whole system as an integrated entity on a small piece of semiconductor intertwined with other systems… Read More

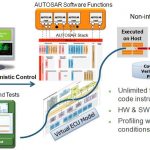

Virtual Platform Powers AUTOSAR Software Development

As a significant part of our life is spent in travelling, it’s natural that automotive sector continues to get traction with a significant push towards electronics and automated solutions for automobiles such as cars to provide safety, comfort and entertainment. These solutions are provided by complete systems which operate… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center