At the end of last week I talked to Sanjiv Kaul, the new CEO of Calypto. Just to give a little background for those that haven’t been following along at home, Calypto was founded to try and solve the very hard problem of sequential logical equivalence checking (mostly by people from the engineering team that I managed at Ambit).… Read More

Author: Paul McLellan

A Brief History of the Foundry Industry, part 2

Part 1 here.

The line between fabless semiconductor companies and IDMs has blurred over the last decade. Back in the 1990s, most IDMs manufactured most of their own product, perhaps using a foundry for a small percentage of additional capacity when required. But their own manufacturing was competitive, both in terms of the capacity… Read More

Reliability is the New Power

It has be come a cliche to say that “power is the new timing”, the thing that keeps designers up at night and drives the major architectural decisions in big SoCs. Nobody is saying it yet but perhaps “reliability is the new power” will be tomorrow’s received wisdom.

I talked to Adrian Evans of IROCTech… Read More

A Brief History of the Foundry Industry, part 1

The fundamental economics of the semiconductor industry are summed up in the phrase “fill the fab.” Building a fab is a major investment. With a lifetime of just a few years, the costs of owning a fab are dominated by depreciation of the fixed capital assets (the building, the air and water purification equipment, the manufacturing… Read More

Lithography from Contact Printing to EUV, DSA and Beyond

I used my secret powers (being a blogger will get you a press pass) to go to the first day of the SPIE conference on advanced lithography a couple of weeks ago. Everything that happens to with process nodes seems to be driven by lithography, and everything that happens in EDA is driven by semiconductor process. It is the place to find … Read More

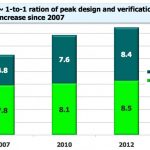

Verification the Mentor Way

During DVCon I met with Steve Bailey to get an update on Mentor’s verification. They were also announcing some new capabilities. I also attended Wally Rhines keynote (primarily about verification of course, since this was DVCon; I blogged about that here) and the Mentor lunch (it was pretty much Mentor all day for me) on the… Read More

Watch the Clock

Clock gating is one of the most basic weapons in the armoury for reducing dynamic power on a design. All modern synthesis tools can insert clock gating cells to shut down clocking to registers when the contents of the register are not changing. The archetypal case is a register which sometimes loads a new value (when an enable signal… Read More

Integrating Formal Verification into Synthesis

Formal verification can be used for many things, but one is to ensure that synthesis performs correctly and that the behavior of the output netlist is the same as the behavior of the input RTL. But designs are getting very large and formal verification is a complex tool to use, especially if the design is too large for the formal tool… Read More

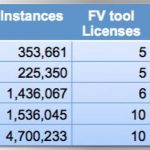

Cavium Adopts JasperGold Architectural Modeling

Cavium designs some very complex SoCs containing multiple ARM or MIPS cores at 32 and 64 bit. This complexity leads to major challenges in validating the overall chip architecture to ensure that their designs will meet the requirements of their customers once they are completed, with performance as high as 100Gbps.

Cavium have… Read More

SoC Derivatives Made Easier

Almost no design these days is created from scratch. Typical designs can contain 500 or more IP blocks. But there is still a big difference between the first design for a new system or platform, and later designs which can be extensively based on the old design. These are known as derivatives and should be much easier to design since… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center