The last of the current series of webinars is on Sentinel-PSI,IC-Package, Power and Signal Integrity Solution. It will be at 11am Pacific time on Thursday 11th August. It will be conducted by Dr. Tao Su, product manager of the Sentinel products. Dr. Su has many years of experience in the EDA industry and is specialized in power integrity… Read More

Author: Paul McLellan

SNUG outside Silicon Valley

SNUG in Silicon Valley was in March so either you were there or you’ve missed it. But it is the summer (and fall) of SNUG in the rest of the world:

SNUG China (in Beijing, Shanghai, Shenzhen) on August 22nd-30th

SNUG Singapore on August 23rd

SNUG Taiwan (in Hsinchu) on August 25-26th

SNUG Japan (in Tokyo) on September 7th

SNUG … Read More

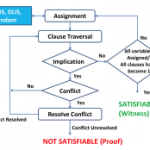

Assertion-based Formal Verification

Formal verification has grown in importance as designs have grown and it has become necessary to face up to the theoretical impossibility of using simulation to get complete coverage along with the practical impossibility of simulating enough to even get close.

There are a number of solvers for what is called satisfiability (SAT)… Read More

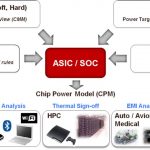

Chip-Package-System Webinar

The webinar on CPS (chip-package-system) is on Tuesday 9th August at 11am Pacific time. It will be conducted by Christopher Ortiz, Principal Application Engineer at Apache Design Solutions. Dr. Ortiz has been with Apache since 2007, supporting the Sentinel product line. Prior to Apache he worked at Agere / LSI, where he investigated… Read More

IC Power Dissipation in…the New York Times!

Generally if you want to read about power dissipation in SoCs and the potential impact on limiting how much computer power we might be able to cram onto a given piece of silicon then EE Times is a good place to look. But last weekend there was a full-length article in, of all places a different Times, the New York Times, entitled Progress… Read More

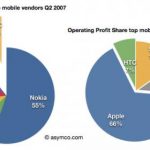

Apple makes 2/3 of profits of entire mobile industry

This is an amazing picture (click to enlarge). Apple now makes 2/3 of all the profit in the entire mobile handset industry. And that is the entire handset industry, not just smartphones where it has also blown past Nokia to become number one (although there are more Android handsets than iOS, those handsets are spread across multiple… Read More

PathFinder webinar: Full-chip ESD Integrity and Macro-level Dynamic ESD

The PathFinder webinar will be at 11am Pacific time on Thursday 4th August. It will be conducted by Karthik Srinivasan, Senior Applications Engineer at Apache Design Solutions. Mr. Srinivasan has over four years of experience in the EDA industry, focusing on die, system, and cross-domain analysis. His professional interests… Read More

Totem webinar: Analog/Mixed-Signal Power Noise and Reliability

The Totem webinar will be at 11am on Tuesday 2nd August. This session will be conducted by Karan Sahni, Senior Applications Engineer at Apache Design Solutions. Karan has been with Apache since 2008, supporting the Redhawk, Totem, Sentinel product lines. He received his MS in Electrical Engineering from the Syracuse University… Read More

Cache Coherency and Verification Seminar

At DAC Jasper presented a seminar with ARM on cache coherency and verification of cache coherency. The seminar is now available online for those of you that missed DAC or missed the seminar itself.

Cache architectures, especially for multi-core architectures, are getting more and more complex. Techniques originally pioneered… Read More

PowerArtist webinar

The next Apache webinar is on PowerArtist, RTL Power Analysis on July 26th at 11am Pacific time. The webinar will be conducted by David “Woody” Norwood, Principal Applications Engineer at Apache Design Solutions. David has been supporting RTL Power products for the past 8 years. He has broad EDA industry experience… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era