Synopsys made significant announcements during the recent TSMC OIP Ecosystem Forum, showcasing a range of cutting-edge solutions designed to address the growing complexities in semiconductor design. With a strong emphasis on enabling next-generation chip architectures, Synopsys introduced both new technologies and … Read More

Author: Kalar Rajendiran

Synopsys and TSMC Pave the Path for Trillion-Transistor AI and Multi-Die Chip Design

Elevating AI with Cutting-Edge HBM4 Technology

Artificial intelligence (AI) and machine learning (ML) are evolving at an extraordinary pace, powering advancements across industries. As models grow larger and more sophisticated, they require vast amounts of data to be processed in real-time. This demand puts pressure on the underlying hardware infrastructure, particularly… Read More

Automating Reset Domain Crossing (RDC) Verification with Advanced Data Analytics

The complexity of System-on-Chip (SoC) designs continues to rise at an accelerated rate, with design complexity doubling approximately every two years. This increasing complexity makes verification a more difficult and time-consuming task for design engineers. Among the key verification challenges is managing reset domain… Read More

Collaboration Required to Maximize ASIC Chiplet Value

It is a well-known fact that chiplets provide several advantages over traditional monolithic chips. Despite these benefits, the transition to a chiplet-based design paradigm presents challenges that need coordinated efforts across the industry. In essence, collaborative efforts among various players involved are not … Read More

Synopsys Powers World’s Fastest UCIe-Based Multi-Die Designs with New IP Operating at 40 Gbps

As the demand for higher performance computing solutions grows, so does the need for faster, more efficient data communication between components in complex multi-die system-on-chip (SoC) designs. In response to these needs, Synopsys has introduced the world’s fastest UCIe-based IP solution, capable of operating at a groundbreaking… Read More

Alphawave Semi Unlocks 1.2 TBps Connectivity for HPC and AI Infrastructure with 9.2 Gbps HBM3E Subsystem

In the rapidly evolving fields of high-performance computing (HPC) and artificial intelligence (AI), reducing time to market is crucial for maintaining competitive advantage. HBM3E systems play a pivotal role in this regard, particularly for hyperscaler and data center infrastructure customers. Alphawave Semi’s… Read More

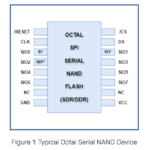

Overcoming Verification Challenges of SPI NAND Flash Octal DDR

As the automotive industry continues to evolve, the demands for high-capacity, high-speed storage solutions are intensifying. Autonomous vehicles and V2X (Vehicle-to-Everything) communication systems generate and process massive amounts of data, necessitating advanced storage technologies capable of meeting these… Read More

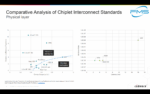

The Impact of UCIe on Chiplet Design: Lowering Barriers and Driving Innovation

The semiconductor industry is experiencing a significant transformation with the advent of chiplet design, a modular approach that breaks down complex chips into smaller, functional blocks called chiplets. A chiplet-based design approach offers numerous advantages, such as improved performance, reduced development … Read More

Mitigating AI Data Bottlenecks with PCIe 7.0

During a recent LinkedIn webcast, Dr. Ian Cutress, Chief Analyst at More than Moore and Host at TechTechPotato, and Priyank Shukla, Principal Product Manager at Synopsys, shared their thoughts regarding the industry drivers, design considerations, and critical advancements in compute interconnects enabling data center… Read More

Alphawave Semi Tapes Out Industry-First, Multi-Protocol I/O Connectivity Chiplet for HPC and AI Infrastructure

In the rapidly evolving landscape of high-performance computing (HPC) and artificial intelligence (AI), the demand for increased processing power, efficiency, and scalability is ever-growing. Traditional monolithic chip designs are increasingly unable to keep pace with these demands, leading to the emergence of chiplets… Read More

Solving the EDA tool fragmentation crisis