Ever since the birth of the semiconductor industry, advances have always been at a fast pace. The complexity of SoCs have grown along the way, driven by the demanding computational and communication needs of various market applications. Over the last decade, the growth in complexity has accelerated at unforeseen rates, fueled… Read More

Author: Kalar Rajendiran

CEVA Accelerates 5G Infrastructure Rollout with Industry’s First Baseband Platform IP for 5G RAN ASICs

The 5G technology market is huge with incredible growth opportunities for various players within the ecosystem. As a leading cellular IP provider, CEVA has been staying on top of the opportunity by offering solutions that enable customers to bring differentiated products to the marketplace. Earlier this year, SemiWiki posted… Read More

Methodology to Minimize the Impact of Duty Cycle Distortion in Clock Distribution Networks

Synchronous circuits dominate the electronic world because clocking eases the design of circuits compared to asynchronous circuits. At the same time, clocking also introduces its share of challenges to overcome. No wonder, a tremendous amount of time and effort have been spent over the years on developing and implementing … Read More

Flex Logix: Industry’s First AI Integrated Mini-ITX based System

As the market for edge processing is growing, the performance, power and cost requirements of these applications are getting increasingly demanding. These applications have to work on instant data and make decisions in real time at the user end. The applications span the consumer, commercial and industrial market segments.… Read More

Truechip: Customer Shipment of CXL3 VIP and CXL Switch Model

The tremendous amount of data generated by AI/ML driven applications and other hyperscale computing applications have forced the age old server architecture to change. The new architecture is driven by the resource disaggregation paradigm, wherein memory and storage are decoupled from the host CPU and managed independently… Read More

Five Key Workflows For 3D IC Packaging Success

An earlier blog started with the topic of delivering 3D IC innovations faster. The blog covered the following foundational enablers for successful heterogeneous 3D IC implementation.

- System Co-Optimization (STCO) approach

- Transition from design-based to systems-based optimization

- Expanding the supply chain and tool

Getting Ahead with Semiconductor Manufacturing Equipment and Related Plasma Reactors

Advanced semiconductor fabrication technology is what makes it possible to pack more and more transistors into a sq.mm of a wafer. The rapidly increasing demand for advanced-process-based chips has created huge market opportunities for semiconductor manufacturing equipment vendors. According to SEMI, worldwide sales … Read More

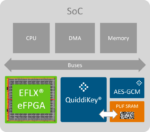

Protecting Critical IP With Next-Generation Zero Trust Security

While semiconductors are the enablers for high-tech solutions, the semiconductor industry was not at the forefront of Cloud adoption. There were many valid concerns behind the slow adoption, a primary reason being the threat to intellectual property (IP) security. IP in this context refers to not just chip building blocks but… Read More

Delivering 3D IC Innovations Faster

3D IC technology development started many years ago well before the slowing down of Moore’s law benefits became a topic of discussion. The technology was originally leveraged for stacking functional blocks with high-bandwidth buses between them. Memory manufacturers and other IDMs were the ones to typically leverage this … Read More

Flex Logix Partners With Intrinsic ID To Secure eFPGA Platform

While the ASIC market has always had its advantages over alternate solutions, it has faced boom and bust cycles typically driven by high NRE development costs and time to market lead times. During the same time, the FPGA market has been consistently bringing out more and more advanced products with each new generation. With very… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?