You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

IoT edge device design means four domains – MEMS, analog, digital, and RF – not only work together, but often live on the same die (or substrate in a 2.5D process) and are optimized for power and size. Getting these domains to work together effective calls for an enhanced flow.

Historically, these domains have not played together … Read More

Anybody who has done any bus & board system design knows the problem. Merchant boards typically have standardized pinouts (after years of haggling in standards organizations) for the backplane bus, and a group of user-defined pins for daughtercard I/O. Homegrown systems usually have a just-as-carefully defined proprietary… Read More

An incredibly pervasive trend at last year’s ARM TechCon was the IoT, and I expect this year to bring even more of the same, but with a twist. Where last year was mostly focused on ultra-low power edge devices and the mbed ecosystem, this year is likely to show a better balance of ideas across all three IoT tiers. I also expect a slew of … Read More

We’ve had several blogs introducing the Juno ARM Development Platform as a vehicle for ARMv8-A software development. S2C has jumped in with a module connecting their FPGA-based prototyping platform to the Juno, enabling more advanced IP… Read More

We periodically see that “software ate the world” line – I’m pretty sure I’ve used it a couple times myself. The fact is, software doesn’t run itself; never has, never will. Somewhere there has to be an underlying computer. First it was on beads, then in gears, then in tubes.… Read More

ARM’s Cortex-M4 processor core represented quite a breakthrough in digital signal controller technology when launched in 2010. Adding a single-cycle multiplier and SIMD instructions enabled basic DSP algorithms while retaining the low power benefits of an MCU. New technology circa 2016 – embedded programmable logic – can… Read More

As SoC design size and complexity increases, simulation alone falls farther and farther behind, even with massive cloud farms of compute resources. Hardware acceleration of simulation is becoming a must-have for many teams, but means more than just providing emulation… Read More

If one wireless IoT technology fit every possible use case, we would have one specification. Many tradeoffs – battery life, mobility, indoor coverage, licensed versus unlicensed spectrum, and more – have made for many potential solutions. A heated discussion right now is over the future of LPWAN technologies, with LoRA, SIGFOX,… Read More

When Steve Jobs made it clear at the 1997 Apple Worldwide Developer Conference he was taking back his company, he tossed the now famous line in his opening monologue: “Focusing is about saying no.” Approaching 20 years later, that decision still reverberates.… Read More

Another report today of a Samsung Galaxy Note 7 catching fire, this time an allegedly refurbished unit, takes us back to the turning point in Samsung mobile phone history. It’s not the first time a defective Samsung phone – or a pile of thousands of them – has been on fire.

Samsung Chairman Lee Kun-Hee issued a powerful edict to his mobile… Read More

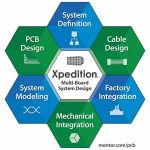

Solving the EDA tool fragmentation crisis