You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

The difficulty of an engineering problem can be gauged by two things:

1) The number of attempts to generate a solution.

2) The degree of hyperbole used to describe the effectiveness of the latest solution.

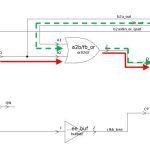

The problem many folks in the EDA industry are after right now is clock domain crossings (CDCs) and the resulting metastability… Read More

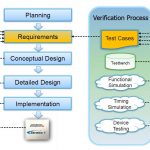

Word association: if I said “requirements management”, you’d probably say IBM Rational “DOORS,” or maybe Serena or Polarion if you come from the IT world. But what if the requirements you need to manage are for an FPGA or ASIC, with HDL and testbench code and waveform files and more details backing verification, and compliance… Read More

A random walk down OS-VVMby Don Dingee on 05-13-2013 at 11:14 amCategories: Aldec, EDA

Unlike one prevailing theory of financial markets, digital designs definitely don’t function or evolve randomly. But many engineers have bought into the theory that designs can be completely tested randomly. Certainly there is value to randomness, exercising all combinations of inputs, including unexpected ones a designer… Read More

Unless you are a small company with one design team, the chance you have standardized on one FPGA vendor for all your needs, forever and ever, is unlikely. No doubt you probably have a favorite, because of the specific class of part you use most often or the tool you are most familiar with, but I’d bet you use more than one FPGA vendor routinely.… Read More

Mentor’s announcement from Design West this week pretty much signals the end of standalone ESL tools, in favor of more useful stuff. They have pulled the pieces of their Sourcery CodeBench environment along with their embedded Linux offering and their Vista virtual prototyping platform into a native embedded software development… Read More

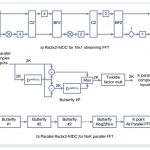

A basic building block of any communication system today is the fast Fourier transform, or FFT. A big advantage of FPGA implementations of FFTs is they can be scaled and tuned for the task at hand, optimizing data flow, resource use, and power consumption. Scaled, that is, up to the clock speed of the FPGA – or so it would seem.

Today’s… Read More

I was trying to find the comment one of my counterparts here made eight months ago that given the cash burn rate, Nokia would be out of business in eight months, so I could gloat a bit. Bzzzzzzt – cash position actually increased in 1Q13. The numbers tell a painful story about a company on a difficult diet to survive, one that analysts… Read More

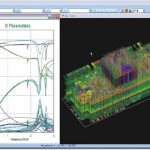

Ground. It’s that little downward-pointing triangle that somehow works miracles on every schematic. It looks very simple until one has to tackle modern power distribution network (PDN) design on a board with high speed and high power draw components, and you soon discover ground is a complicated fairy tale with a lot of influences.… Read More

When Cadence acquired Sigrity in 2012, two motives were involved: get more competitive in state of the art signal integrity analysis, and grab a foothold into the other vendor’s PCB flows in an area that is developing as a real sore spot for digital designers.

Just as the days where PCB tape-out meant actually using tape are over, … Read More

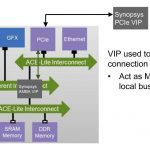

So, you dropped that piece of complex IP you just licensed into an SoC design, and now it is time to fire up the simulator. How do you verify that it actually works in your design? If you didn’t get verification IP (VIP) with the functional IP, it might be a really long day.

Compliance checking something like a PCIe interface block is a … Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?