After a four year gestation period typical of global communications standards, G.fast has reached the point where chipset makers can implement parts against stable specifications. Formal approval of the physical layer spec, G.9701, is expected by the end of 2014. G.9700, dealing with power spectral density issues, was approved… Read More

Author: Don Dingee

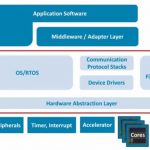

3 reasons to focus on hardware dependent software

Why is software for modern SoCs so blasted expensive to develop? One reason is more software is being developed at the kernel layer – hardware dependent software, or HdS. Application software often assumes the underlying hardware, operating system, communication stacks, and device drivers are stable. For HdS, this flawed assumption… Read More

i.am, I said

The tie between rock artists and technology isn’t new. One of the first prominent rockers-turned-entrepreneurs is Tom Scholz of Boston, an engineer who has a couple MIT degrees and several patents to his name. Neil Young is currently out with Pono, attempting to make a higher-resolution audio format based on FLAC encoding to get… Read More

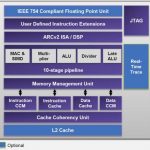

Linux and the ARC of the Coherent

Remember that thing called “real-time Linux”? Yeah, nobody else does either. As builds became configurable and clock speeds increased, embedded Linux manifested itself as fast enough for many applications – if a few other SoC details are addressed.

Most obvious for SoCs to run Linux is the need for a fully integrated MMU implementation.… Read More

Did we forget non-volatile memory?

In our rush to shrink SoC nodes more and more to achieve better performance and more complex devices, we may have forgotten a passenger in the back seat: non-volatile memory. There has been little discussion of this in the pages of SemiWiki until now. Let’s give it a closer look.

Embedded flash has usually been associated with microcontrollers,… Read More

NoC resilience protects end-to-end

Protecting memory with ECC but leaving the rest of an SoC uncovered is like having a guard dog chained up in the back corner of your yard. If the problem happens to be in that particular spot, it’ll be dealt with, otherwise there will be a lot of barking but little actual protection.

Similarly, adding a safety-capable processor like… Read More

A de-parallel universe for Windows 10

It was CES 2011 when Steve Ballmer sweatered up and pitched the coming universe according to Microsoft, where the same Windows base would run on everything – PC, phone, tablet, and game console. Getting from that visionary statement to Windows 10 hasn’t been a smooth ride.… Read More

Cortex-M7: 6-stage, cached, 400 MHz MCU

“Who needs a 32-bit MCU?” It was a question asked a million times in the press when ARM introduced the Cortex-M family back in 2004. In fairness, that question predates the Internet of Things, with wireless sensor networks, open source code, encryption, and more needs for connected devices.… Read More

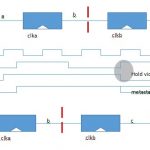

Dominating FPGA clock domains and CDCs

Multiple clock domains in FPGAs have simplified some aspects of designs, allowing effective partitioning of logic. As FPGA architectures get more flexible in how clock domains, regions, or networks are available, the probability of signals crossing clock domains has gone way up.… Read More

Explaining HAPS-DX in an elevator

Every development team has been through this challenge: finding a tool that looks fantastic, then heading off to the manager one or two levels up who has enough signature authority for the purchase order. Signatures for amounts reading more than a couple of trailing zeros on POs are rarely free, or painless. … Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!