A few years back before IoT became the buzzword, the industrial automation community had already talking about “smart sensors” since the mid-1990s. The impetus for those discussions was IEEE 1451, a family of standards for adding intelligence and wireless communications to sensors so they could be incorporated into field networks.… Read More

Author: Don Dingee

Loving it when a Qualcomm plan comes together

Corporate layoffs are always a touchy subject. I think that’s because there is skepticism that one round of layoffs can turn into two, then if business still doesn’t improve the spiral accelerates into more rounds. Too many rounds indicate management didn’t really have a clue what was going on in the business, instead trying to … Read More

Can one process handle IIoT safety and security?

SemiWiki had another article recently making the case that in IoT applications, safety and security are intertwined, adding that both are important, but they are not the same thing. Mentor Graphics has weighed in with a new white paper trying to tie both issues to a methodology.

Industrial IoT – or IIoT as you’ll often see in shorthand… Read More

Not-so-ulterior motive leads SoftBank to ARM

This week’s £24.3B offer for ARM Holdings plc from SoftBank has been widely viewed as Brexit reflexit. It did firm up in the preceding two weeks, but this acquisition offer has been years in the making – and if it sticks, one SoftBank motive many analysts and editors are missing comes front and center.… Read More

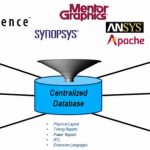

10 Challenges in IP Design Collaboration

Enterprise design management can be summed up in one word: collaboration. Intellectual property (IP) reuse and the success of distributed system-on-chip (SoC) design efforts depend strongly on how well designers can collaborate. As time-to-market windows have shortened, the challenges around design collaboration have… Read More

Webinar alert – Hybrid prototyping for ARMv8

All the talk about ARM server SoCs has been focused on who will come up with the breakthrough chip design. Watching trends like OPNFV develop suggests the big breakthrough is more likely to come on the ARMv8 software side. How do you quickly validate ARMv8 software when you don’t have the exact ARMv8 SoC target?… Read More

Time-saving modules expand Prototype Ready family

A big advantage of FPGA-based prototyping is the ability to run real-world I/O at-speed, significantly faster and more accurately than hardware emulation systems typically requiring a protocol adapter. Dealing with real-world I/O means more thorough verification of SoC integration, and the opportunity to optimize systems… Read More

RISC-V opens for business with SiFive Freedom

When we talk about open source, free usually comes in the context of “freedom”, not as in “free beer”, and open IP often serves as a base layer of value add for commercialization. The creators of the RISC-V instruction set, now working at startup SiFive, have released specifications for their aptly-named Freedom processor IP cores… Read More

Latest Pinpoint Release Tackles DRC and Trend Lines

After reading previous SemiWiki coverage on Dassault Systèmes and their ENOVIA Pinpoint solution, one big item seemed missing: how does this thing actually work? With all due respect to our other bloggers who covered when Dassault Systèmes acquired Pinpoint from Tuscany Design Automation, why Qualcomm is using Pinpoint, and… Read More

21 months lining up OPNFV-on-ARM for telecom

Telecom infrastructure is one area where X86 architecture hasn’t dominated historically. Infrastructure gear is spread across MIPS, Power, and SPARC architectures, with some X86, and a relative newcomer: ARM, already claiming 15% share. That’s a stunning figure considering only a bit less than 5 years ago… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era