The IEEE has an Orange Country Chapter of the Components, Packaging and Manufacturing Technology Society who are organizing an all-day workshop, 3D Integrated Circuits: Technologies Enabling the Revolution. This looks to be an informative day with real-world examples in both design and test being presented by over a dozen … Read More

Author: Daniel Payne

Physical Verification of 3D-IC Designs using TSVs

3D-IC design has become a popular discussion topic in the past few years because of the integration benefits and potential cost savings, so I wanted to learn more about how the DRC and LVS flows were being adapted. My first stop was the Global Semiconductor Alliance web site where I found a presentation about how DRC and LVS flows were… Read More

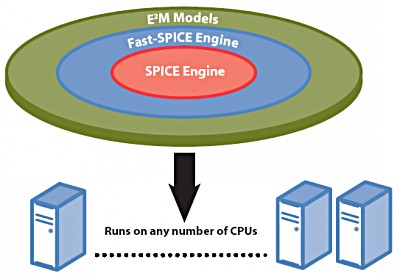

SPICE Circuit Simulation at Magma

All four of the public EDA companies offer SPICE circuit simulation tools for use by IC designers at the transistor-level, and Magma has been offering two SPICE circuit simulators:

- FineSIM SPICE (parallel SPICE)

- FineSIM PRO (accelerated, parallel SPICE)

An early advantage offered by Magma was a SPICE simulator that could be … Read More

Learning Verilog for ASIC and FPGA Design

Verilog History

Prabhu Goel founded Gateway Design Automation and Phil Moorby wrote the Verilog language back in 1984. In 1989 Cadence acquired Gateway and Verilog grew into a de-facto HDL standard. I first met Prabu at Wang Labs in 1982 where I designed a rather untestable custom chip named the WL-2001 (yes, it was named to honor… Read More

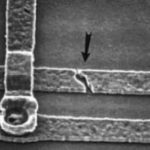

What’s New with Semiconductor Test and Failure Analysis at Mentor?

ISTFA

Silicon Valley is a great location for trade shows and technical conferences, so if you have an interest in test and failure analysis then don’t miss out on the 37th annual International Symposium for Testing and Failure Analysis. This year ISTFA will be held from Sunday, November 13th thru Thursday, November 17th … Read More

AMS Design using Dongbu HiTek foundry and Tanner EDA Tools

Every analog designer needs a foundry PDK (Process Design Kits) and EDA tools to design, layout and verify their AMS chip or IP. This week I had a chance to conduct an email interview with Taek-Soo Kim, VP of Technical Engineering at Dongbu HiTek in Korea. This specialty foundry supplies analog silicon worldwide.

Interview

Q: Tell… Read More

Oct 27 – Hands-on Workshop with Calibre: DRC, LVS, DFM, xRC, ERC (Fremont, California)

I’ve blogged about the Calibre family of IC design tools before:

Smart Fill replaced Dummy Fill Approach in a DFM Flow

Graphical DRC vs Text-based DRC

Getting Real time Calibre DRC Results with Custom IC Editing

Transistor-level Electrical Rule Checking

AMS Design at AnSem

AnSem has been in the AMS design business since 1998 and uses a variety of commercial EDA tools along with internally developed tools and scripts to automate the process of analog design and technology porting. Their IC designers have completed some 40 AMS projects in diverse areas like:

- RF CMOS

- LNA, VCO, Mixers

- Synthesizers

- Low-IF/Zero-IF

Mentor at the TSMC Open Innovation Platform Ecosystem Forum

EDA companies and foundries must closely collaborate in order to deliver IC tool flows that work without surprises at the 40nm and 28nm nodes.

Tomorrow in San Jose you can attend this 4th annual event hosted by TSMC along with Mentor Graphics and other EDA and IP companies.

Here are some of the topics that will interest IC designers… Read More

EDA and ITC

Every SOC that is designed must be tested and the premier conference for test is ITC, held last month in Anaheim, California.

I spoke with Robert Ruiz of Synopsys by phone on September 21st to get an update on what is new with EDA for test engineers this year. Robert and I first met back at Viewlogic when Sunrise was acquired in the 90’s.… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?