Joe Sawicki is the VP and General Manager at Mentor Graphics for the Design-to-Silicon Division where the Calibre product line is developed. We met today in Wilsonville, Oregon to review the challenges in IC design, processing and manufacturing.… Read More

Author: Daniel Payne

Clock Design for SOCs with Lower Power and Better Specs

Dan Ganousis posted in our SemiWiki forums about a newer technique to lower the power consumed by GHz clocks on SOC designs and asked if I was interested to learn more, so we met today via WebEx. Dan is with a company called Cyclos Semiconductor, co-founded in 2006 by Marios Papaefthymiou, President and Alexander Ishii, VP of Engineering.… Read More

MEMS layout and automation

At a webinar today I listened and learned about how a tool called L-Edit can be used to layout MEMS designs plus automate the task to be more productive. I can see how the history of IC layout editing is now being repeated with MEMS because in the earliest IC layout tools we could only do manual entry of polygons, then gradually we got cells… Read More

Learning About MEMS

My automobile has an air bag system that uses a MEMS (Micro Electro Mechanical System) sensor to tell it when to deploy, and I’ve read headlines talking about MEMS over the years so I decided it was about time to learn more by attending a Webinar on Wednesday, December 14th at 8AM Pacific Time.

The EDA company hosting the Webinar… Read More

How Fast (and accurate) is Your SPICE Circuit Simulator?

In my dad’s generation they tweaked cars to become hotrods while in EDA today we have companies that tweak SPICE circuit simulators to become crowned speed champions. The perennial question though is, “How fast and accurate is my SPICE circuit simulator?”… Read More

Methodics can Now use www.methodics.com after Domain Name Battle in EDA

Imagine trying to run your EDA business only to have a competitor squat on your domain name and then make disparaging remarks about you. This sounds like a match made for reality TV however it is quite real, and now this chapter in EDA has a happy ending because Methodics can use www.methodics.com as their domain name.

The Bad Guy

We’ve… Read More

EDA mergers: Accelicon acquired by Agilent

Agilent acquired EEsof back in 1999, now the EEsof group acquired Accelicon on December 1, 2011. The terms of the deal are not disclosed.

SPICE circuit simulators are only as accurate as their models and algorithms. On the model side we have Accelicon that provides EDA tools to create SPICE models based on silicon measurements:… Read More

HSPICE – I Didn’t Know That About IC Circuit Simulation

HSPICE is over 30 years old, which is a testimony of how solid the circuit simulator has been and how widely used it is. To stay competitive the HSPICE developers have to innovate or the product will slowly loose ground to the many other simulator choices. I listened to the webinar last week to find out what was new with HSPICE.

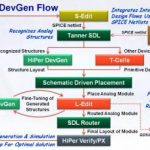

A Review of an Analog Layout Tool called HiPer DevGen

My last IC design at Intel was a Graphics Chip and I developed a layout generator for Programmable Logic Arrays (PLA) that automated the task, so I’ve always been interested in how to make IC layout more push-button and less polygon pushing. Today I watched a video about HiPer DevGen from Tanner EDA and wanted to share what I … Read More

December 1st – Hands-on Workshop with Calibre: DRC, LVS, DFM, xRC, ERC (Fremont, California)

I’ve blogged about the Calibre family of IC design tools before:

Smart Fill replaced Dummy Fill Approach in a DFM Flow

DRC Wiki

Graphical DRC vs Text-based DRC

Getting Real time Calibre DRC Results with Custom IC Editing

Transistor-level Electrical Rule Checking

Who Needs a 3D Field Solver for IC Design?

Prevention is Better… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!