At the DAC show in June I met with folks at Berkeley DA and heard about their Analog Fast SPICE simulator being used inside of the Tanner EDA tools. With the newest release from Tanner called HiPer Silicon version 15.23 you get a tight integration between:… Read More

Author: Daniel Payne

ASIC Prototyping with 4M to 96M Gates

I’ve used Aldec tools like their Verilog simulator (Riviera PRO) when teaching a class to engineers at Lattice Semi, so to get an update about the company I spoke with Dave Rinehart recently by phone. A big product announcement by Aldec today is for their ASIC prototyping system with a capacity range of 4 Million to 96 Million… Read More

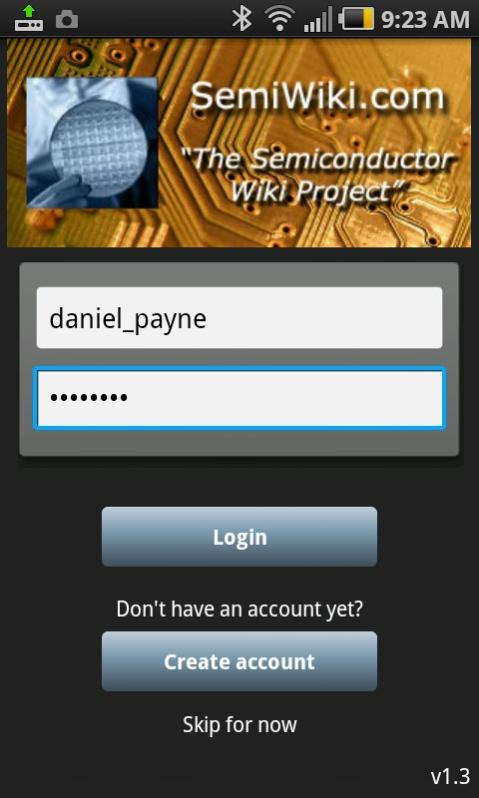

SemiWiki on Android

This morning I got to try out the new Android app for SemiWiki, so this is something that you will benefit from as you’re on the go with an Android phone and want to stay up to date. It’s an intuitive app, so you’ll be up and running within minutes. My first step was to visit the Play Store, search for the app using “Semiwiki”,… Read More

Custom IC and AMS Tool Flow with Synopsys

The big three EDA companies all have Custom IC and AMS tool flows as shown in the following comparison table:… Read More

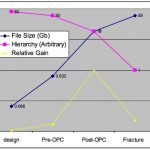

The Need for OASIS in Post-layout IC Databases

OASIS is a hierarchical IC file format used for IC designs that is gradually replacing GDS II throughout the mask data stages. The compelling reason for using OASIS has always been the reduction of file size, and speed up of processing times through the use of hierarchy and fewer translation steps.

At the 45nm node an actual M1 layer… Read More

Mixed-Signal Methodology Guide

Last week I reviewed Chapter 1 in the new book: Mixed-Signal Methodology Guide, and today I finish up my review of Chapters 2 through 11. You can read the entire book chapter by chapter, or just jump directly to the chapters most related to your design role or project needs. With multiple authors I was impressed with the wide range of… Read More

Mixed-Signal Methodology Guide

Last week I reviewed Chapter 1 in the new book: Mixed-Signal Methodology Guide, and today I finish up my review of Chapters 2 through 11. You can read the entire book chapter by chapter, or just jump directly to the chapters most related to your design role or project needs. With multiple authors I was impressed with the wide range of… Read More

Book Review: Mixed-Signal Methodology Guide

Almost every SoC has multiple analog blocks so AMS methodology is an important topic to our growing electronics industry. Authored by Jess Chen (Qualcomm), Michael Henrie (Cliosoft), Monte Mar (Boeing) and Mladen Nizic (Cadence), the book is subtitled: Advanced Methodology for AMS IP and SoC Design, Verification and Implementation… Read More

Book Review: Mixed-Signal Methodology guide

Almost every SoC has multiple analog blocks so AMS methodology is an important topic to our growing electronics industry. Authored by Jess Chen (Qualcomm), Michael Henrie (Cliosoft), Monte Mar (Boeing) and Mladen Nizic (Cadence), the book is subtitled: Advanced Methodology for AMS IP and SoC Design, Verification and Implementation… Read More

ARM + Broadcom + Linux = Raspberry Pi

Broadcom has designed an impressive SOC named the BCM2835 with the following integrated features:

- ARM CPU at 700MHz

- GPU – VideoCore IV

- RAM – 256 MB

The British chaps at Raspberry Pi have created a $35.00 Linux-based computer based on the Broadcom BCM2835 chip that is tiny in size but big in utility:… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?