I first started using WordPress in 2008 after having written my own Content Management System (CMS) to build and manage web sites. WordPress is the number one CMS in the world, is just 10 years old, and is used by over 70 million users. What got me thinking about WordPress and EDA software companies was a recent book by Scott Burken, … Read More

Author: Daniel Payne

IC Layout with Interactive or Batch DRC and LVS Results

IC designers have a long tradition of mixing and matching EDA tools from multiple vendors, mostly because they enjoy best-in-class tools, or they just purchased each EDA tool at a different time and asked for them to work together. Such is this case with IC layout tools from Silvacoand DRC/LVS tools from Mentor Graphics. Pawan Fangaria… Read More

Key Ingredients for ESL Power Modeling, Simulation, Analysis and Optimzations

There’s a French EDA company named DOCEA Powerthat is uniquely focused on power analysis at the ESL level and I had a chance to interview Ridha Hamza to get new insight on ESL design challenges and their approach. Ridha started out doing SRAM design at STMicroelectornics in the 1990’s, moved into the emerging field … Read More

Automating PCB Timing Closure, Saving Up to 67%

The benefits of using EDA software is that it can automate a manual process, like PCB timing closure, saving you both time and engineering effort. This point was demonstrated today as Cadenceadded new timing-closure automation to their Allegroproduct family, calling it Allegro TimingVision. On Tuesday I spoke with Hemant Shah… Read More

What I Didn’t Know about Electronic Design Automation

I started using internal EDA tools at Intel beginning in 1978 and have worked in the commercial EDA industry since 1986, so it was a delight to read a chapter about EDA in Nenni and McLellan’s newest book: Fabless – The Transformation of the Semiconductor Industry. Starting in the 1970’s the authors talk about… Read More

A Brief History of Chip Design at Apple Computer

Steve Wozniak in 1976 designed the Apple 1 while working at HP during the daytime, and he used standard parts to keep costs low, like:

- 6502 CPU from MOS Technology

- 8K of DRAM

- TTL logic for driving video and random logic

- PROM to hold the BASIC language and primitive OS

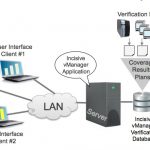

SoC Functional Verification Planning and Management Goes Big

Big SoC designs typically break existing EDA tools and old methodologies, which then give rise to new EDA tools and methodologies out of necessity. Such is the case with the daunting task of verification planning and management where terabytes of data have simply swamped older EDA tools, making them unpleasant and ineffective… Read More

A Methodology for Assertion Reuse in SoC Designs

As your SoC design can contain hundreds of IP blocks, how do you verify that all of the IP blocks will still work together correctly once assembled? Well, you could run lots of functional verification at the full-chip level and hope for the best in terms of code coverage and expected behavior. You could buy an expensive emulator to … Read More

Before SPICE Circuit Simulation Comes TCAD Tools

I’ve run SPICE circuit simulators since the 1970’s and they use transistor models where the device parameters are provided by the foundry. These transistor and interconnect parameters come from an engineer at the foundry who has characterized silicon with actual measurements or by running a TCAD (Technology CAD)… Read More

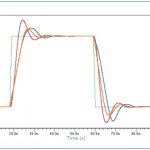

Speeding Up AMS Verification by Modeling with Real Numbers

My first introduction to modeling an AMS behavior using a language was back in the 1980’s at Silicon Compilers using the Lsim simulator. Around the same time the VHDL and Verilog languages emerged to handle the modeling of both digital and some analog behaviors. The big reason to model analog behavior with a language is for… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!