With High-Level Synthesis (HLS) the first benefit that comes to my mind is reduced design time, because coding with C or SystemC is more efficient than low-level RTL code. What I’ve just learned is that there’s another benefit, a reduction in the amount of functional simulation required. One HLS customer was able … Read More

Author: Daniel Payne

Verification IP for PCIe and AXI4

Engineers love acronyms and my latest blog post has three acronyms in the title alone, so hopefully you are doing or considering SoC designs with the AMBA AXI4(Advanced eXtensible Interface 4) interface specification along with PCI Express (Peripheral Component Interconnect Express). One big motivation for using semiconductor… Read More

Webinar: Choosing IP for your next IoT Design

My favorite IoT device is a cycle-computer from CatEyeand it has GPS for tracking my bike routes, and an LCD display that shows me speed, cadence, heart rate and time. After each ride I connect my CatEye device to a USB connector, upload my data to Strava.com, and then see how I’m doing versus other cyclists and my own personal… Read More

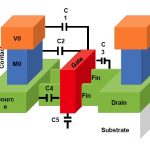

FinFET Design Enablement

We read about FinFET technology in the semiconductor press daily now, thanks to Intel introducing their TriGate transistors starting in 2011 and creating a race with foundries and IDMs to switch from planar CMOS nodes. To get some perspective about the progress of FinFET IP and EDA tools I spoke with two experts from Synopsys, Swami… Read More

Apple Watch Announcement

Rock music, invitation only tickets, hollywood lighting, journalists from around the world, live streaming on the web, yes, another typical Apple-orchestrated product launch on Monday, March 9th at the Yerba Buena Center in California.

Up first was a video about Apple’s store opening in West Lake China with superb cinematography.… Read More

Blogging for Consultants

Paul McLellan wrote about how he stumbled into blogging and it inspired me to share my story as well. I grew up in Minnesota and attended the U of Minnesota earning a bachelor’s degree in Electrical Engineering so that I could design computer chips. After interviewing in 1978 with HP, IBM, Intel and Motorola I decided to join… Read More

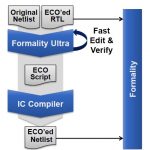

Faster ECOs Using Formal Analysis

Your latest SoC has just begun the tape-out process and then marketing comes back with a small update to the specification to make your design more competitive, or maybe your regression tests just found a minor bug in a single IP block that needs to be fixed. Should you go back in your design flow, change the RTL source code and then completely… Read More

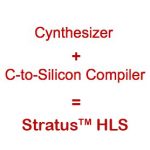

High Level Synthesis Gets Stronger

High Level Synthesis (HLS) tools have been around for at least two decades now, and you may recall that about one year ago Cadence acquired Forte. The whole promise of HLS is to provide more design and verification productivity by raising the design abstraction from RTL code up to SystemC, C or C++ code. With any acquisition it is natural… Read More

Product Review: Google Chromecast

Our household members own both Apple and Android devices, so we wanted a way to share our photos or videos on the Samsung TV. The device we ended up buying is called Chromecast from Google, and it’s a small media streaming device that plugs into an HDMI port on our TV. We’ve had Chromecast for about six weeks now.… Read More

More Test Points are Better

I got really involved in testability back at CrossCheck in the 1990’s when they designed a way for Gate Arrays to have 100% observability without any Design For Test (DFT) requirements on designers. The Japanese Gate Array companies loved this approach and their customers enjoyed the highest test coverage without being… Read More

Why Your LLM-Generated Testbench Compiles But Doesn’t Verify: The Verification Gap Problem