One holy grail of AI software developers is to create a system that is self-aware, or sentient. A less lofty goal than sentient AI is for chip designers to know how each specific chip responds to Process variations, Voltage levels and Temperature changes. If a design engineer knew exactly which process corner that each chip was fabricated… Read More

Author: Daniel Payne

Hierarchy Applied to Semiconductor IP Reuse

When I first started doing IC design back in 1978 we had hierarchical designs, and that was doing a relatively simple 16Kb DRAM chip with only 32,000 transistors using 6um (aka 6,000 nm) design rules. SoC designs today make massive use of hierarchy at all levels of IC design: IC Layout, transistor netlist, gate level netlist, RTL … Read More

Protecting electronics around the world, SEMI insights

SEMI is a worldwide organization with local chapters like the one here in Oregon, where I attended a recent half-day presentation by several industry experts on the topic – Globalization, How it shapes the Semiconductor industry:

- Michael Chen, Director, Mentor – A Siemens Business

- John Brewer, CEO, Amorphyx

- Ed

A Brief History of PSS at Breker

Verification engineers are hearing a lot about the Portable Stimulus Standard (PSS), and for good reason because it could potentially save them time and effort in doing their jobs much better. In order to get the big picture on what PSS is all about I contacted Adnan Hamid, founder and CEO of Breker Verification Systems, because … Read More

12 Year-old Semiconductor IP and Design Services Company Receives New Investment

I have a transistor-level IC design background so was intrigued to learn more from the CEO of an IP and services company that started out in India 12 years ago. Last week I spoke with Samir Patel, CEO of Sankalp Semiconductorabout the newest $5 million financial investment in his company from Stakeboat Capital Fund. The Stakeboat… Read More

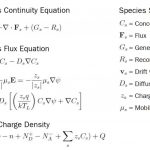

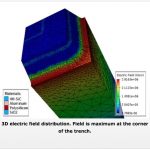

Using a TCAD Tool to simulate Electrochemistry

In college I took courses in physics, calculus, chemistry and electronics on my way to earn a BSEE degree, then did an 8 year stint as a circuit designer, working at the transistor level and interacting with fab and test engineers. My next adventure was working at EDA companies in a variety of roles. As a circuit designer I knew that … Read More

1st Annual International Conference, Semiconductors ISO 26262

When we talk about the promise of ADAS and autonomous cars then along the way we also hear about this functional safety standard called ISO 26262 which semiconductor companies all pay close attention to. I recently learned about a new conference called Semiconductors ISO 26262, scheduled for December 5-7 in Munich, Germany. The… Read More

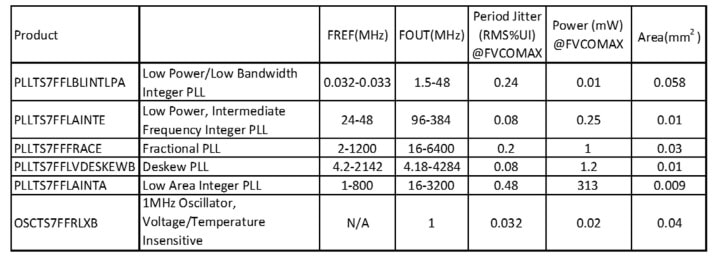

Silicon Creations talks about 7nm IP Verification for AMS Circuits

Designing at 7nm is a big deal because of the costs to make masks and then produce silicon that yields at an acceptable level, and Silicon Creations is one company that has the experience in designing AMS IP like: PLL, Serializer-Deserializer, IOs, Oscillators. Why design at 7nm? Lots of reasons – lower power, higher speeds,… Read More

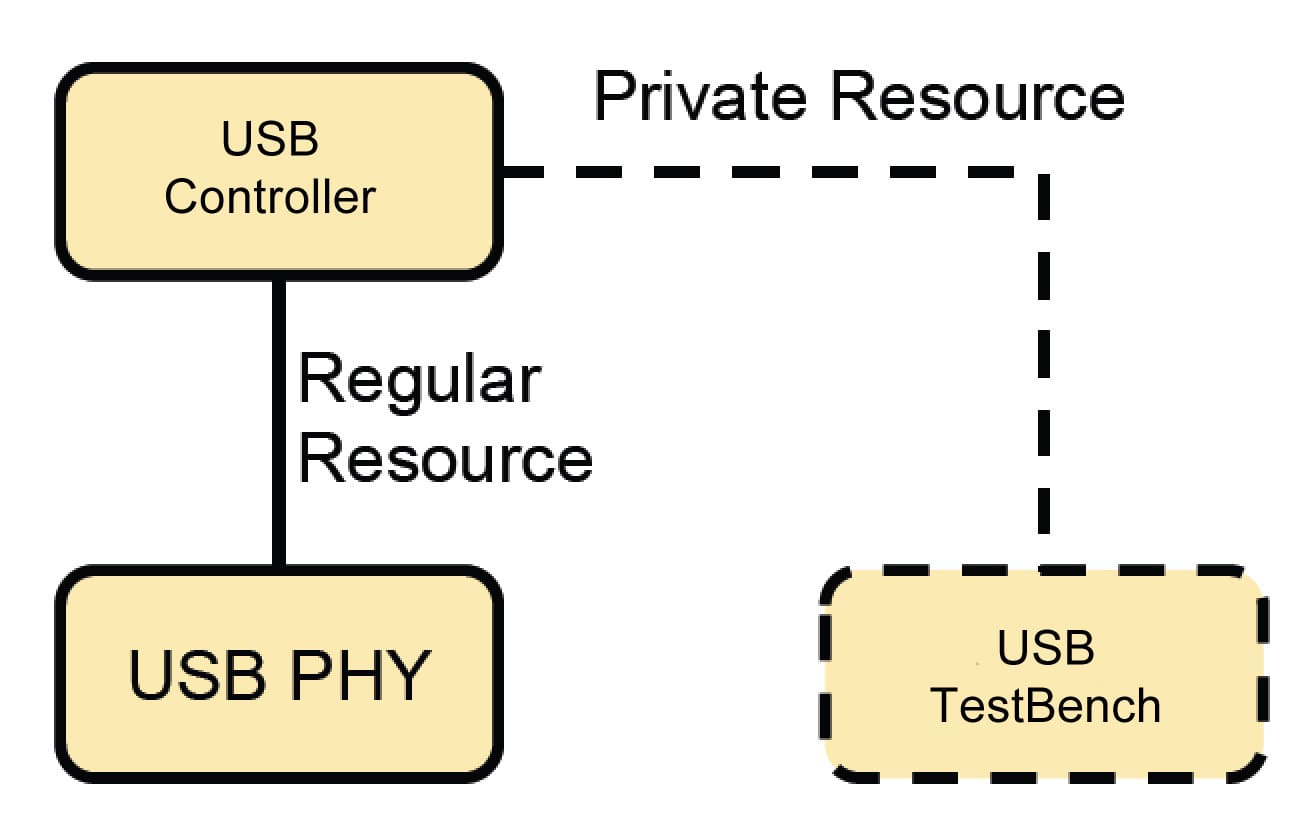

Rethinking IP Lifecycle Management

We recently saw both Apple and Samsung introduce new smart phones, and realize that the annual race to introduce sophisticated devices that are attractive and differentiated is highly competitive. If either of these companies misses a market window then fortunes can quickly change. SoCs with billions of transistors like smart… Read More

Webinar on Electrochemistry and how it affects Semiconductor devices

My educational background is Electrical Engineering and I’ve learned a lot since starting in the industry back in 1978 while working on bipolar, NMOS and CMOS technology, designing DRAM, data controller and GPU devices. I continue to learn about the semiconductor industry through daily reading and attending trade shows… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?