I love starting a new project from scratch, because there’s that optimistic feeling of having no constraints and being able to creatively express myself and get the job done right this time. For SoC designs today there are teams of engineers and maybe a program manager plus a marketing person that define the features, budget… Read More

Author: Daniel Payne

Automating the Analysis of Power MOSFET Designs

There’s a world of difference between our smart phones that are battery powered and pack billions of transistors, and power MOSFET devices that can be used in industrial applications, telecom, cloud computing and automotive where they could be run at a few hundred volts and up to 80A of current. I’ve read about one … Read More

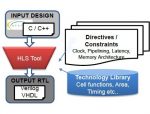

High-Level Synthesis and Open Source Software Algorithms

The DVCon conference and exhibition finished up in California just as the impact of the COVID-19 pandemic was ramping up in March, but at least they finished the conference by altering the schedule a bit. Umesh Sisodia, CEO at CircuitSutra Technologies presented at DVCON on the topic, Using High-Level Synthesis to Migrate Open… Read More

Webinar: Real-time In-Chip Monitoring to Boost multi-core AI, ML, DL Systems

During the COVID-19 pandemic I’m using Zoom and attending more webinars to keep updated on semiconductor industry trends, and one huge trend is the importance of AI applied to SoCs. Using more cores to handle ML and DL makes sense, but then how do you keep the chips within their power and reliability limits while at the same … Read More

CEO Interview: Jason Xing of Empyrean Software

It’s been about seven years since Randy Smith last interviewed Jason Xing, the President/CEO of North America for Empyrean Software, so the timing felt good for a fresh update. I’ve been watching Empyrean at DAC for several years now, and have come away impressed with their growth and focus on some difficult IC design… Read More

Project-Centric Design Process, or IP-centric

How do most IC design teams organize their work during the design process?

Most design teams would say that they organize their work into a project-centric view, and that at the beginning of the process use a tool for requirements management, maybe a bug tracker, or some design management tool. On the four IC designs that I worked … Read More

Mixed-Signal Debugging Gets a Boost

Having the right tool for the job at hand is always a joy, and when your IC project involves RTL code, gates, transistors and even parasitic interconnect, then you need some EDA tool help for debugging and finding out why your design behaves the way it is. An FAE named Sujit Roy did a conference call with me last week to show what StarVision… Read More

Viewing the Largest IC Layout Files Quickly

The old adage, “Time is money”, certainly rings true today for IC designers, so the entire EDA industry has focused on this challenging goal of making tools that help speed up design and physical verification tasks like DRC (Design Rule Checks) and LVS (Layout Versus Schematic). Sure, the big three EDA vendors have… Read More

DVCon Is a Must Attend Event for Design and Verification Engineers

Learning is a never-ending process for design and verification engineers, so outside of reading SemiWiki you likely want to attend at least a few events per year to keep updated, learn something new, attend a workshop, or even present something that has made your IC project work much better than before. Sure, DAC is always a great… Read More

Cycling and CES 2020

It’s a new year, so time to share with you all things cycling being shown at CES. Yes, most of CES is devoted to new TV displays, futuristic automobiles, all things 5G, laptops and mobile phones, but there’s a growing segment of consumer products for fitness, and cycling happens to be my fitness passion. Riding a bike … Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?