Many types of designs, including analog designs, MEMs, and image sensors, require electrically matched configurations. This symmetry has a huge impact on the robustness of the design across process variations, and its performance. Having an electrically matched layout basically means having a symmetric layout. To check … Read More

Author: Daniel Payne

Automating and Optimizing an ADC with Layout Generators

I first got involved with layout generators back in 1982 while at Intel, and about 10% of a GPU was automatically generated using some code that I wrote. It was an easy task for one engineer to complete, because the circuits were digital, and no optimization was required. In an IEEE paper from the 2022 18th International Conference… Read More

Fast EM/IR Analysis, a new EDA Category

I’ve watched the SPICE market segment into multiple approaches, like: Classic SPICE, Parallel SPICE, FastSPICE and Analog FastSPICE. In a similar fashion the same thing just happened to EM/IR analysis, because after years of waiting we finally have a different approach to EM/IR analysis that works at the top-level of … Read More

EDA in the Cloud with Siemens EDA at #59DAC

Tuesday at DAC I had the pleasure of attending the Design on Cloud Theatre where experts from Siemens EDA gave an update on what they’ve been offering to IC and systems designers. I remember attending a cloud presentation from Craig Johnson in 2021, so I was keen to note what had changed in the past 12 months.

Industry Trends,

… Read MoreAxiomise at #59DAC, Formal Update

Monday at DAC I was able to meet with Dr. Ashish Darbari, the CEO and founder of Axiomise. Ashish had a busy DAC, appearing as a panelist at, “Those Darn Bugs! When Will They be Exterminated for Good?”; and then presenting, “Taming the Beast: RISC-V Formal Verification Made Easy.”

I had read a bit about Axiomise… Read More

Calibre, Google and AMD Talk about Surge Compute at #59DAC

In 2022 using the cloud for EDA tasks is a popular topic, and at DAC this year I could see a bigger presence from the cloud hardware vendors in the exhibit area, along with a growing stampede of EDA companies. Tuesday at DAC there was a luncheon with experts from Siemens EDA, Google and AMD talking about surge compute. I already knew Michael… Read More

New Mixed-Signal Simulation Features from Siemens EDA at DAC

It’s the second day of DAC, and the announcements are coming in at a fast pace, so stay tuned to SemiWiki for all of the latest details. As a long-time SPICE user and industry follower, I’ve witnessed the progression as EDA vendors have connected their SPICE simulators to digital simulators, opening up a bigger world… Read More

What’s New With Calibre at DAC This Year?

When I worked at EDA vendors and attended DAC, one of the most popular questions asked in the booth and suites was simply, “What’s new this year?” It’s a fair question, and yet many semiconductor professionals are so focused on their present project, using their familiar methodology, that they simply… Read More

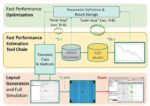

Using AI in EDA for Multidisciplinary Design Analysis and Optimization

Most IC and system engineers follow a familiar process when designing a new product: create a model, use parameters for the model, simulate the model, observe the results, compare results versus requirements, change the parameters or model and repeat until satisfied or it’s time to tape out. On the EDA side, most tools perform… Read More

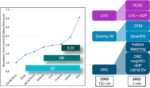

Using IP-XACT, RTL and UPF for Efficient SoC Design

The ESD Alliance collects and reports every quarter the revenue trends for both EDA and Semiconductor IP (SiP), and the biggest component for the past few years has been the SiP, as IP re-use dominates new designs. For Q4 of 2021 the total SiP revenue was $1,314.3 Million, enjoying a 24.8% growth in just one year. Here’s a chart… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?