Standards committees, the military and governmental organizations are drawn to acronyms as moths are drawn to a flame, though few of them seem overly concerned with the elegance or memorability of these handles. One such example is SOTIF – Safety of the Intended Function – more formally known as ISO/PAS 21448. This is a follow-on… Read More

Author: Bernard Murphy

Breker on PSS and UVM

When PSS comes up, a lot of mainstream verification engineers are apt to get nervous. They worry that just as they’re starting to get the hang of UVM, the ivory tower types are changing the rules of dynamic verification again and that they’ll have to reboot all that hard-won UVM learning to a new language. The PSS community and tool … Read More

Getting to EMC Compliance by Design

At the risk of highlighting my abundant lack of expertise in the domain, I had always viewed EMC (electromagnetic compatibility) compliance and testing as one of those back-end exercises that can only be done on the real device and depends on a combination of expertise and brute-force in chip/package/module/system design (decaps,… Read More

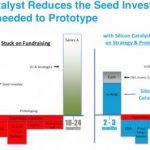

Re Energizing Silicon Innovation

Hardware is roaring back into prominence in technology innovation, from advanced cars to robots, smart homes and smart cities, 5G communication and the burgeoning electronification of industry, medicine and utilities. While software continues to play a role, all of these capabilities depend fundamentally on advances in … Read More

Anirudh Keynote at CDNLive 2019

Anirudh Devgan (President of Cadence), gave the third keynote at CDNLive Silicon Valley this year. He has clearly become adept in this role. He has a big, but supportable vision for Cadence across markets and technologies and he’s become a master of the annual tech reveals that I usually associate with keynotes.

Anirudh opened … Read More

Compute at the Edge

At first glance, this seems like a ho-hum topic- just use whatever Arm or RISC-V solution you need – but think again. We’re now expecting to push an awful lot of functionality into these edge devices. Our imaginations don’t care about power, performance and cost; everything should be possible so let’s keep adding cool features.… Read More

Foundational Excellence in a Laid-Back Style

I recently had a call with Rob Dekker, Founder and CTO of Verific. If you’re in EDA or semiconductor CAD, chances are high that you know who they are. They’re king of the hill in parser software for SystemVerilog and VHDL. When you hear a line like that, you assume a heavy dose of marketing spin, but here it really is fact. I don’t know of… Read More

ML and Memories: A Complex Relationship

No, I’m not going to talk about in-memory-compute architectures. There’s interesting work being done there but here I’m going to talk here about mainstream architectures for memory support in Machine Learning (ML) designs. These are still based on conventional memory components/IP such as cache, register files, SRAM and various… Read More

Hogan Fireside Chat with Paul Cunningham at ESDA

If you’re in verification and you don’t know who Paul Cunningham is, this is a guy you need to have on your radar. Paul has risen through the Cadence ranks fast, first in synthesis and now running the verification group, responsible for about a third of Cadence revenue and a hefty percentage of verification tooling in the semiconductor… Read More

Lip-Bu Keynote at CDNLive 2019

Cadence CEO Lip-Bu Tan is always an interesting guy to listen to for his broader technology industry overview and his insight into emerging tech through his Walden International investments. Though we’re usually heads-down in challenging technical problems, it’s good to look up from time to time to check whether what … Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?