During Q&A session at San Jose GTC 2018, nVidia CEO Jen-Hsun Huang reiterated that critical functional safety, such as in autonomous vehicle, requires both the redundancy and the diversity aspects. For example, CUDA with Tensor core and GPU with DLA were both utilized. Safety is paramount to automotive applications. Any… Read More

Author: Alex Tan

Functional Safety Methodologies for Automotive Applications

Meeting the Challenges of National Defense Strategy

In February this year, the Department of Defense (DoD) submitted a $686.1 billions budget for 2019 and published a National Defense Strategy outlining the overall spending for defense and military programs. The recently signed US $1.3 trillion spending bill included part of the funding. According to DoD Defense Budget Overview… Read More

Aart de Geus At the Heart of Impact!

At the Silicon Valley SNUG 2018, Synopsys Chairman and co-CEO Dr. Aart de Geuss gave his keynote speech addressing attendees on how far we have evolved, and at times encountered the aha factor that helps propel us to the next level. He explored trends as well as the current state of his company solution offerings.

Moore’s Law, Digital… Read More

FPGA, Data and CASPA: Spring into AI (2 of 2)

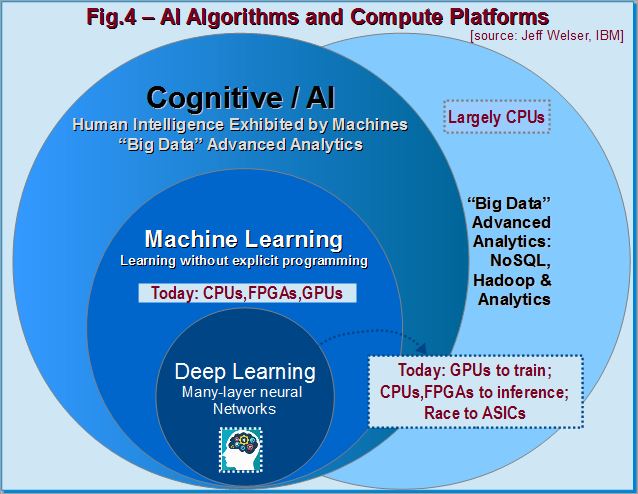

Adding color to the talks, Dr. Jeff Welser, VP and IBM Almaden Research Lab Director showed how AI and recent computing resources could be harnessed to contain data explosion. Unstructured data growth by 2020 would be in the order of 50 Zetta-bytes (with 21 zeros). One example, the Summit supercomputer developed by IBM for use at… Read More

FPGA, Data and CASPA: Spring into AI

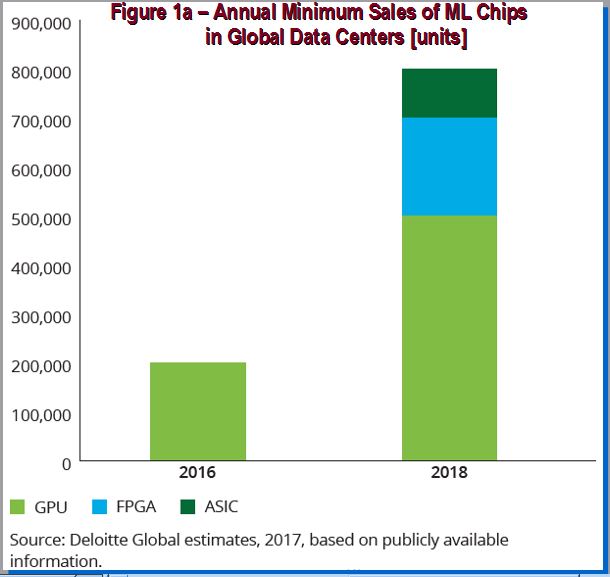

Just like good ideas percolate longer, we have seen AI adoption pace picking-up speed, propelled by faster GPUs. Some recent data points provide good indication that FPGA making a comeback to bridge chip-design needs to keep-up with AI’s ML applications.

According to the Deloitte research firm there is a projected increase of… Read More

Don’t Stand Between The Anonymous Bug and Tape-Out (Part 2 of 2)

The second panel is about system coverage and big data. Coverage metrics have been used to gauge the quality of verification efforts during development. At system level, there are still no standardized metrics to measure full coverage. The emergence of PSS, better formal verification, enhanced emulation and prototyping techniques… Read More

Clock Domain Crossing in FPGA

Clock Domain Crossing (CDC) is a common occurrence in a multiple clock design. In the FPGA space, the number of interacting asynchronous clock domains has increased dramatically. It is normal to have not hundreds, but over a thousand clock domains interactions. Let’s assess why CDC is a lingering issue, what its impact and the … Read More

Don’t Stand Between The Anonymous Bug and Tape-Out (Part 1 of 2)

In the EDA space, nothing seems to be more fragmented in-term of solutions than in the Design Verification (DV) ecosystem. This was my apparent impression from attending the four panel sessions plus numerous paper presentations given during DVCon 2018 held in San Jose. Both key management and technical leads from DV users community… Read More

EDA and Semiconductor — Is There Growth In The Ecosystem?

The semiconductor industry has gone through several major transitions driven by different dynamics such as shift in business models (fab-centric to fab-less), product segmentation (system design house, IP developers) and end market applications (PC to cloud; and recently, to both automotive and Internet of Things — IOT’s,… Read More

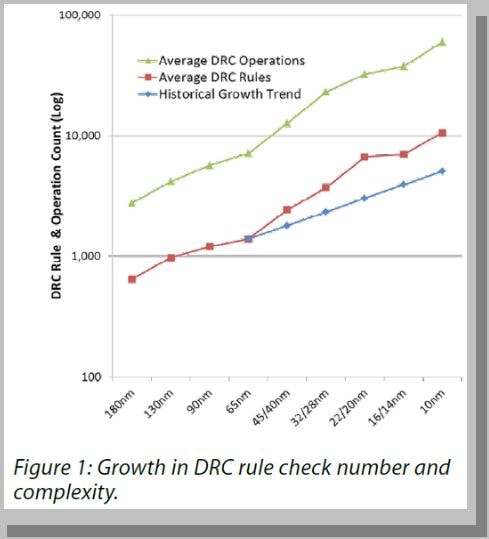

Robust Reliability Verification – A Critical Addition To Baseline Checks

Design process retargeting is acommon recurrence based on scaling orBOM(Bill-Of-Material) cost improvement needs. This occursnot only with the availability of foundry process refresh to a more advanced node,but also to any new derivative process node tailored towards matching design complexity, power profile or reliability… Read More

Breker Hosts an Energetic Panel on Spec-Driven Verification