In a discussion with Tom Fitzpatrick of Siemens EDA he recalled that their Verification Horizons newsletter started 17 years ago, back when they were Mentor. We’ve known about the Siemens acquisition for a while. The deal closed in March 2017, but it wasn’t until January 1, 2021 that the legal entity merger was complete. Which makes this the first version of the newsletter in which they’ve had enough time to absorb and express a Siemens slant to Verification Horizons.

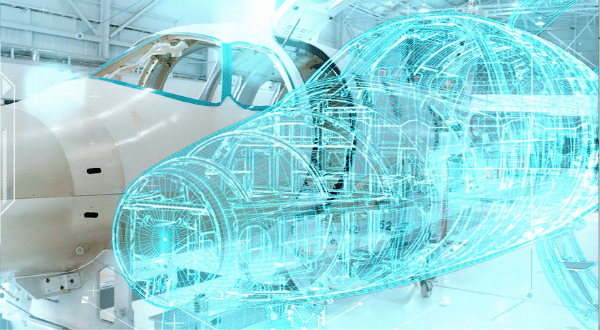

Tom reiterated that a major motivation in the acquisition was filling out the Siemens vision of digital twins. These start from a big system view (like an aircraft for example). Mechanical, fluidics, thermal, software and so on. In modern systems there’s now so much new electronic content that modeling must also reach down inside those subsystems. The September issue of Verification Horizons covers multiple topics underlying this trend. I’ll just touch on a few.

Digital Threads, Twins, MBSE and IC Development

Model-based Systems Engineering (MBSE) is a new favorite topic of mine, driving modeling and design all the way from the ultimate system (e.g. an aircraft) down to SoCs. Siemens outlines a methodology called Arcadia which they use in their System Modeling Workbench to describe and decompose from high-level requirements and block functions down to individual components. SysML is a modeling language commonly used to describe behaviors and constraints at these higher levels.

How does IC design and particularly verification interact with these higher levels? In the example shown in the newsletter, they bridge using TLM (i.e. software) models for IC component behaviors, and verification of requirements through coverage analysis. In the aircraft example, they talk about a DO-254 list of requirements, each requiring a test and confirmation that the test passed. To this they would add coverage metrics to complete requirements coverage.

Verifying AI-enabled SoCs for HPC

Time to market pressures are just as active today in these SoCs as elsewhere, even though such systems are monsters and require very extensive hardware and software testing. (Much of what they describe in this article applies equally to big non-AI systems but I’m guessing this write up was motivated by an actual AI design experience 😀.) They talk here particularly about need for parallel development of hardware and software. This starts from a virtual platform and progresses to IP RTL development in parallel with driver development, and so on through to pre-silicon prove-out with apps and post-silicon bring-up.

The article makes the point that this style of development must be supported by a combination of emulation and prototyping. Emulation through hardware design development and early software apps development, since even here validation must comprehend hardware test loads. Prototyping during late hardware development and through software app development because there you need software performance. The article stresses the advantages of the Siemens two-part prototyping solution here: Veloce Primo for up to 12B gates and ICE support and Veloce ProFPGA for shipping prototypes to customers.

Verifying a DDR5 Memory Subsystem

I like talking about applications, so this is my last selection from the set of articles in the September newsletter. High bandwidth memory is more commonly integrated in big server processors, AI systems and other large SoCs. For this we we need even faster links from the main digital die(s) to these in-package DRAMs. The latest released standard here is DDR5, providing double the bandwidth at lower power than DDR4.

Siemens provides QVIPs for both chip and DIMM DDR5 memories. This write-up goes into quite a bit of detail on connecting and configuring your design. Plus creating compile and simulation scripts and running simulation and debug. I won’t attempt to summarize these other than to note they provide help in generating scenarios. Also assertions, transaction, performance analysis and more. If this is an area of interest to you, follow the link. They provide much more detail on all of these topics.

Lots of good material in this issue of Verifications Horizons. Tom also created his own blog post. Both well worth your time to read!

Also Read:

Optimize AI Chips with Embedded Analytics

AMS IC Designers need Full Tool Flows

Symmetry Requirements Becoming More Important and Challenging

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.