This is a live panel with industry experts who are on the leading edge of AI in semiconductor manufacturing. This is a must attend event for all levels of semiconductor professionals. I hope to see you there.

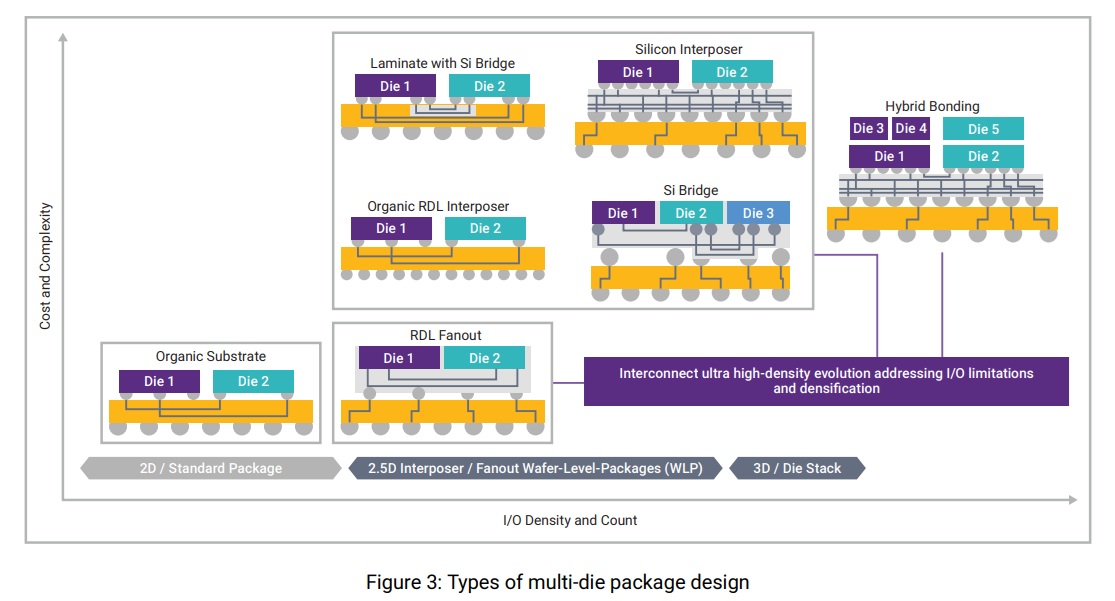

The semiconductor industry faces unprecedented challenges as it pushes toward advanced nodes below 3nm, managing exponential… Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea