This month we’ve seen both Apple and Samsung announce their newest, flagship smart phones, and they each have an incredible number of sensors and components included like:

- Accelerometer

- Mqgnetometer

- Gyroscope

- Proximity

- Altimeter

- Compass

- Near Field Communication

- Fingerprint

- Touchscreen

- ADC

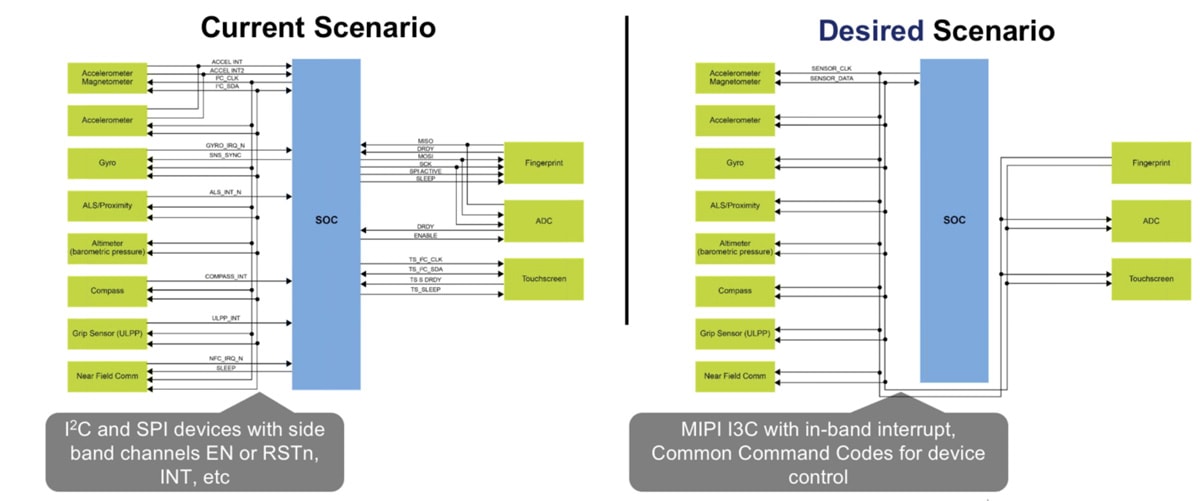

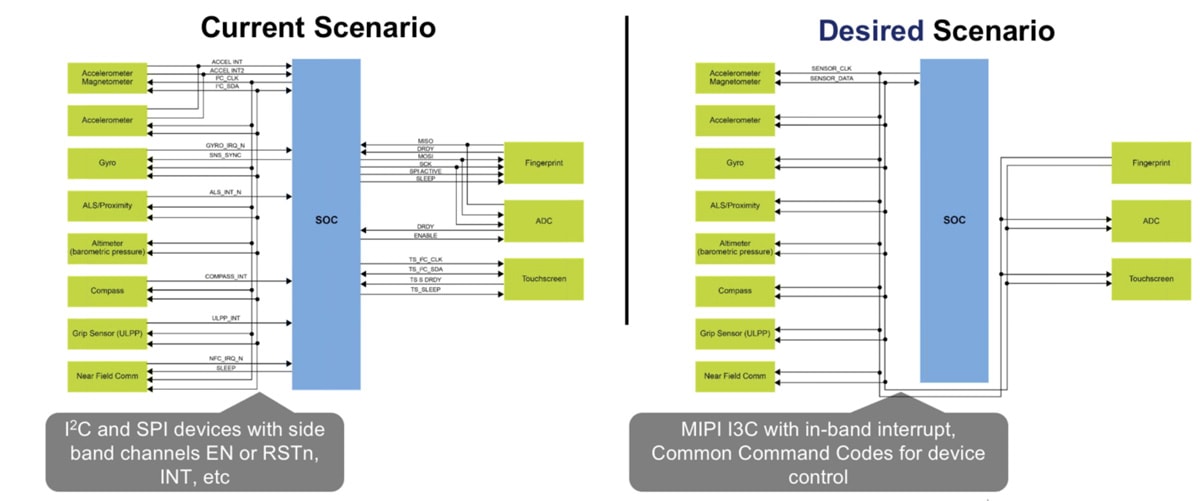

So one engineering challenge is how to most efficiently connect all of these components to an SoC with a minimum of wires and control signals required. The good news is that the MIPI Alliance has figured this out and created the I2C bus interface used by many SoC design companies, and even better news is that the successor called I3C is now available. Paul Kimelman from NXP spoke last week in a webinar all about I3C and how it is upwardly compatible with the previous I2C bus interface. Mr. Kimelman is one of the primary spec authors for I3C, along with Qualcomm and Intel. Other I3C spec contributors include: Invensense, TI, STMicroelectronics, Synopsys, Cadence, Mentor, Sony, Knowles and Lattice Semi,

So what does I3C give you beyond I2C?

The answer: Fewer GPIO wires, higher data speeds, backwards compatibility, standard IO pads, lower power usage. Here’s a quick comparison chart between I2C and I3C features:

[table] style=”width: 600px”

|-

| Feature

| I2C

| MIPI I3C

|-

| Clock Speed & Data Rate

| Fast mode: 400kb/s

Fast mode+: 1Mb/s

High speed: 3.4Mb/s

| SDR: Up to 11Mbps actual Data rate

HDR-DDR: 20Mbps actual data rate

HDR-TSP: ~30Mbps actual data rate

|-

| # wires

| 2 – multi-drop

SCL: Clock – from master(s), slaves stretch

SDA: data – bidirectional

| 2 – multi-drop

SCL: clock – from current Master only

SDA: data – bidirectional

|-

| Power

| High due to open-drain SCL, SDA with strong pullups

| Lower due to SCL being push-pull only and SDA working in push-pull most of the time

|-

| Slave Read Termination

| Master has to end Read

| Slave ends Read, but Master may terminate early

|-

| In-Band Interrupts

| None – use a separate wire/pin per slave

| Integrated, prioritized and may include a byte of context

|-

| Hot-Plug

| None – proprietary systems only

| Built-in. Same mechanism as in-band-interrupt

|-

| Error detection

| No protocol inherent error detection

| Master and slave side error detection standardized, mandated

|-

| Time stamping

| Has to be done by Master once separate INT signal is triggered

| Is an essential part of the spec, no dedicated INT signal required

|-

| Built-in Commands

| None. Proprietary messages only

| Built-in for control, discovery, bus management, etc.

|-

| Master/Slave

| Master-Slave, Multi-master optional

| Master-Slave, Master handoff

|-

| IO pads

| I2C special pads

| Standard pads 4 mA drive

|-

| Slave address

| Static

| Dynamically assigned during initialization. Slaves may have I2C static addresses at start

|-

| Clocking

| Slaves use inbound clock or oversampling

| Slaves use inbound clock

|-

| Complexity

| Low for Slaves. Higher for Masters

| Full Slaves ~2K gates

Masters ~2.5K gates State machine or processor implementations

|-

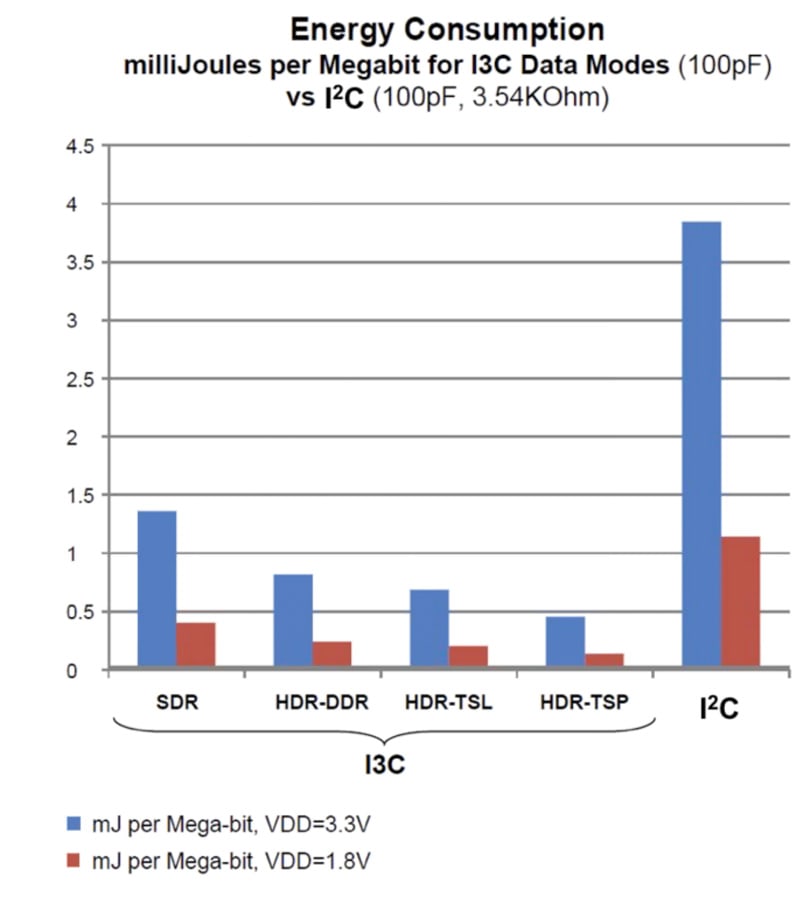

With I3C you can expect lower power by 3 to 8X depending on data rates:

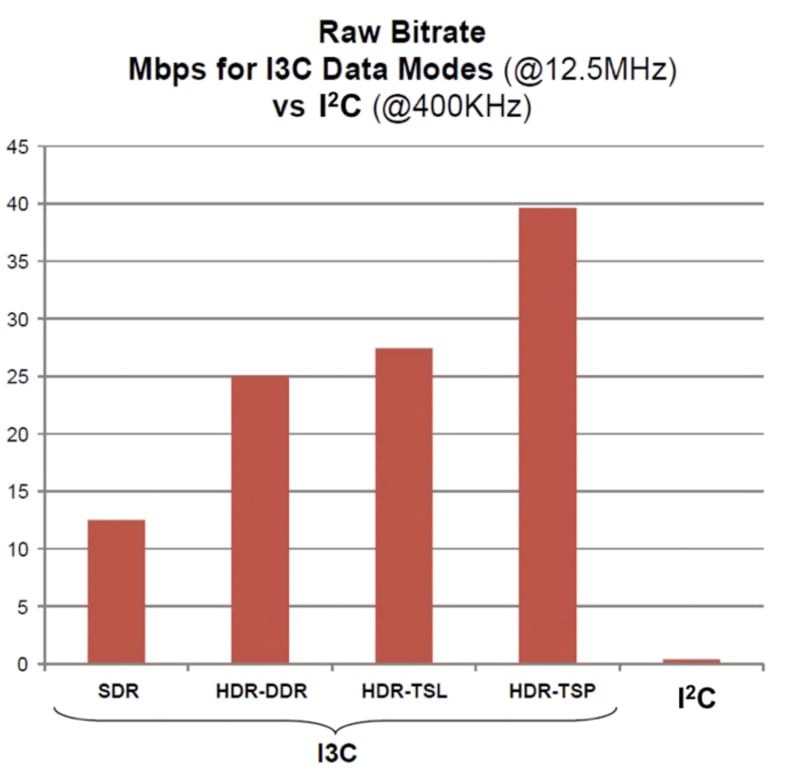

Data rates are greatly increased with I3C compared to I2C, and this chart shows the four raw bitrates possible:

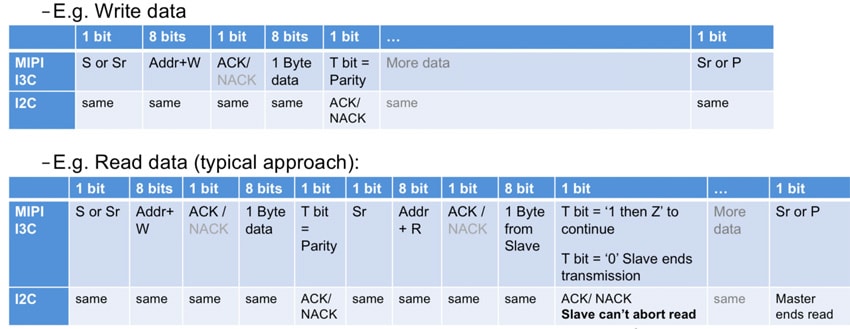

Write and read data for a I3C message look similar to I2C message:

Address arbitration is updated with I3C for use in:

- In-band interrupt

- Hot-join

- Bus initialization to assign dynamic addresses

- Multi-master requestThe I3C specification is at version 1.0 today, however if you want to see what’s coming up next in version 1.1 the list includes:

- Group addressing

- Multi-lane

- In-band HW reset

- HDR-DDR mode Slave side Write termination

- HDR-TSP mode ability to terminate data transfer

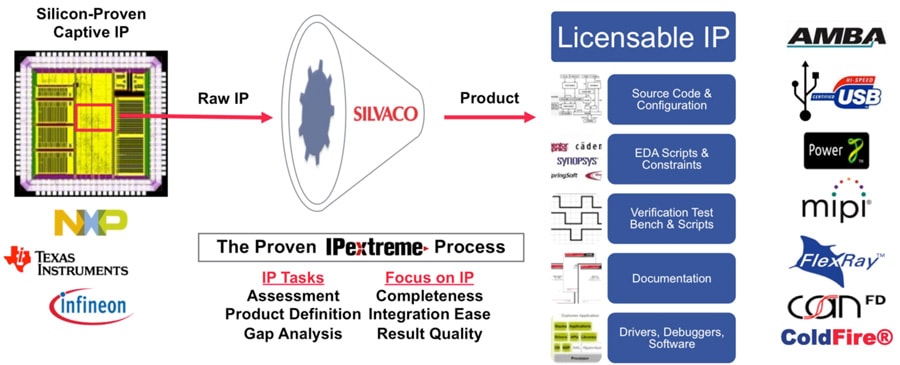

Warren Savage from Silvaco spoke next about semiconductor IP and how IPextreme (acquired by Silvaco) has worked with NXP for the past 10 years to make captive IP into licensable IP. Using that approach NXP has some 50 IP products now.

The applications for I3C are quite diverse into multiple industries:- Medical

- Wearables

- Touchscreen

- Automotive sensors

- Audio

- Home automation

- Instruments

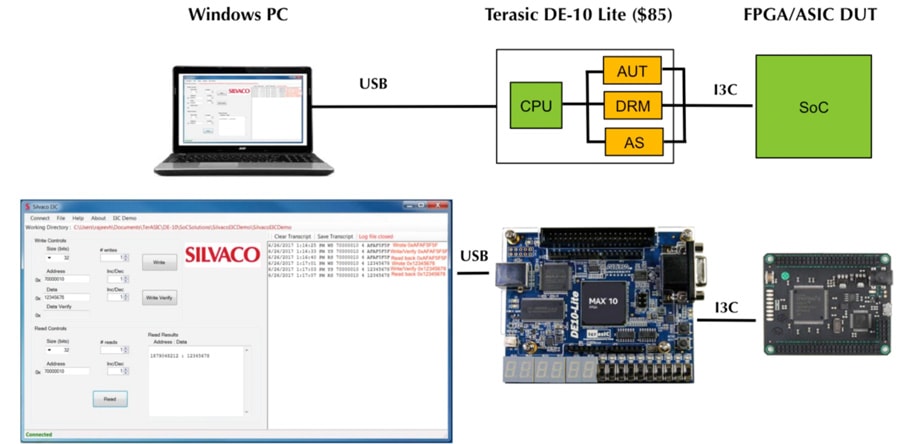

You can even get UVM-based VIP (Verification IP) from Avery Design Systems as an add-on. Silvaco also offers you an FPGA debug environment to test out your I3C compatibility.

Webinar

You can watch the complete webinar, lasting about an hour including the Q&A session online here. I’m really impressed at how effective the MIPI Alliance has been in creating both the I2C and I3C standards for our SoC community to leverage, resulting in consumer and industrial products delivered in record time.

![SILVACO 051525 Webinar 400x400 v2[62]](https://semiwiki.com/wp-content/uploads/2025/04/SILVACO_051525_Webinar_400x400_v262.jpg)

Comments

There are no comments yet.

You must register or log in to view/post comments.