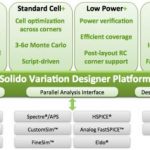

Process variation has been a top trending term since SemiWiki began as a result of the articles, wikis, and white papers posted on the Solido landing page. Last year Solido and TSMC did a webinar together, an article in EETimes, and Solido released a book on the subject. Process variation is a challenge today at 28nm and it gets worse at 20nm and 16nm so you had better be ready.

Solido and TSMC recently completed qualification of Solido Variation Designer for 20-nm memory and standard cell designs. Solido’s software provides accurate, scalable and verifiable 6-sigma design coverage on TSMC 20-nm designs in orders-of-magnitude fewer simulations than Monte Carlo analysis.

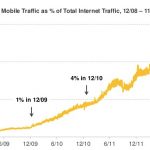

Memory bitcells and sense amps are the first design blocks to take advantage of each shrink in process technology. Transistors are now so small that atomic variances directly impact design variation. Monte Carlo, as the standard for statistical analysis, has not been able to scale to the demands of memory design. Alternate solutions are inaccurate, scale poorly and are difficult to verify.

Consider a 256 Mb SRAM design, which consists of 256M bitcells and 64k sense amps. For the SRAM to yield, the bitcell yield would need to be 6-sigma, and sense amp yield would need to be 4.5-sigma. However, verifying to this sigma would need billions of Monte Carlo samples which is far too slow.

Solido’s High-Sigma Monte Carlo (HSMC) was shown to overcome the key drawbacks of traditional Monte Carlo analysis, providing:

- Significantly fewer simulations

- SPICE and Monte Carlo accurate results in the regions of interest

- Scalable support on all design blocks used in memory design

- Verification, for high confidence in results

Solido’s System Monte Carlo adds yield analysis capability at the array level:

- Providing fast 3-sigma analysis across the array

- Leveraging probability density function (PDF) data from cell-level analysis

- Reporting tradeoffs between performance and yield

- Fast enough to enable exploration of different array configurations

Results of running Solido on TSMC 20-nm memory design:

- Measured bitcell performance to 6.15 sigma

- Analyzed 12.8 billion Monte Carlo samples in only 5355 simulations

- Measured sense amp performance to +/- 4.5 sigma

- Analyzed 3.2 Million MonteCarlo samples in only 2727 simulations

- Extracted probability density function (PDF) of bitcell and sense amp

- Measured Monte Carlo based yield on a 64Mb array for 6 different read speeds in 1.5 hours

- Improved memory specs by 11% to 52%

Retargeting standard cell libraries to new technologies is expense. It takes lots of simulator licenses and design time, layout has become part of the design loop, and increasing variability makes it difficult to size cells optimally for yield and performance. High-sigma analysis is necessary for the latest process technologies, but needs too many Monte Carlo samples to achieve accuracy and extrapolation with fewer samples is unreliable and inaccurate.

Cell Optimizer adds automation for sizing standard cells, providing:

- Full script-based operation

- Design sizing across multiple corners and testbenches

- Support for pre- and post-layout netlists

- Simulator independence

On the initial TSMC 20-nm standard cell design, 3 out of 4 measurements failed to meet the specification. After sizing, all measures met specification.

Signup for a DAC demo here:

Solido Design Automation Inc. is a leading provider of variation-aware custom integrated circuit design software. Solido Variation Designer and application packages are used by analog/RF, IO, memory and standard cell digital library designers to improve design performance, parametric yield and designer productivity. Solido has pioneered a proprietary and patent-pending set of algorithms forming the core of its technology.

lang: en_US