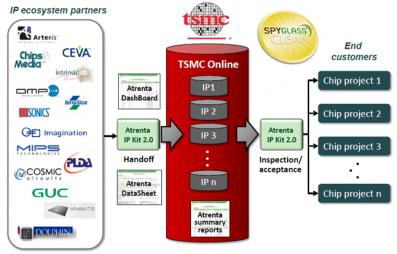

More than one year old now, TSMC’s soft IP quality assessment program is a joint effort between TSMC and Atrenta to deploy a series of SpyGlass checks that create detailed reports of the completeness and robustness of soft IP. This soft IP quality program has been the first to be initiated by a Silicon foundry on other than “Hard IP”, and is demonstrating how IP support, whether hard or soft, is important in TSMC strategy to best support their customers and shorten the design to Silicon delay and reduce the TTM. Currently, over 15 soft IP suppliers have been qualified through the program, including ARM, as recently announced by TSMC at ARM TechCon.

How does the flow works? Atrenta’s SpyGlass® platform provides a powerful combination of proven design analysis tools with broad applicability throughout the SoC flow. The SpyGlass platform includes a tool suite for linting, CDC verification, DFT, constraints analysis, routing congestion analysis and power management applicable at RTL as well as the gate level. Providing visibility to design risks early and at high design abstractions, SpyGlass enables Early Design Closure® –During the course of chip development, design goals evolve and get refined from the initial RTL development phase to the final SoC implementation phase. The SpyGlass platform offers a consistent solution that can be used effectively at each stage of the design process to achieve the respective design goals. The use of the right SpyGlass tools at the right stage of design development helps design teams achieve a predictable repeatable methodology.

The list of design goals addressed by GuideWare, a set of pre-packaged methodologies for SpyGlass, show that the risk of failure is early addressed, and can be minimized:

- Will the design simulate correctly?

- Are clocks and resets defined correctly?

- Will the design synthesize correctly? Are there unintended latches or combo loops?

- Will gate simulations match RTL simulations?

- What will the test coverage be?

- What is the power consumption of a given block?

- What is the profile of this IP? (For example, gates, flops, latches, RAMS/ROMS, I/Os, tristates, clocks)

- Are there any inherent risks or non-standard design practices used in this IP?

- Are there any adaptation issues in the target SoC, such as power, routability or congestion?

- Are all the incoming blocks truly ready for integration? Are they clean in terms of clocks/resets and constraints?

- What are possible inter-block issues? (For example, are block-level constraints complete and coherent with target SoC constraints?)

- What are “common-plane” issues among heterogeneous blocks? (For example, scan chain management and test blockages at the SoC level)

- Can I leverage my block-level work (waivers, constraints) at the SoC level?

Coming back to TSMC soft IP quality assessment program, we can see that the list of IP partners is a who’s who including from Network-on-Chip IP vendor Arteris, DSP IP core supplier CEVA, PCI Express IP core (PLDA), configurable CPU IP core (Tensilica) to GPU and CPU IP core vendors with ARM Ltd. and Imagination Technologies, Video and Display IP (Chips and Media), and scanning also Dolphin Integration, Cosmic Circuits or GlobalUniChip, provider of mixed-signal IP. That’s really make sense that ARM, the #1 IP vendor, join this program, as well as it would really makes sense that at least two of the top 3 EDA & IP vendor, Cadence and Synopsys, would join the program, sooner or later…

Eric Esteve from IPNEST

Share this post via:

Comments

0 Replies to “ARM adopting SpyGlass IP Kit, joining TSMC’s soft IP9000 Quality Assessment Program”

You must register or log in to view/post comments.