Competition in EDA is absolutely necessary in order for the fabless semiconductor ecosystem to thrive. AMS tools with a low learning curve, high interoperability, and a powerful user interface improve design team productivity and enable a low total cost of ownership. That is why Tanner EDA has shipped over 33,000 licenses of its software to more than 5,000 customers in 67 countries. I work closely with Tanner EDA as a liaison between the foundries and the top fabless semiconductor companies so this interview was more like a conversation between friends:

Q: What are the specific design challenges your customers are facing?

Before we discuss design challenges, it may be helpful to share bit about our diverse customer base. We’re coming into our 25[SUP]th[/SUP] year in EDA and we’re seeing some consistent themes across a majority of our customers:

- Core application domains include power management, imagers, life sciences, automotive systems, displays, consumer electronics, sensors and MEMS,

- Users of our layout tool (L-Edit) are actively working at process nodes down to 20nm,

- Users of our entire A/MS tool flow are typically designing at 90nm and above, and

- Common foundry partners include specialty fabs like TowerJazz, XFab, and Dongbu as well as high volume fabs such as TSMC and Globalfoundries.

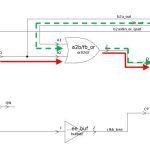

As far as design challenges go, we partition them based on workflow. We have customers using our entire tool suite and we have customers who choose to integrate selected Tanner EDA tools with other point tools. We find that the challenges are very closely related to the part of the design flow a customer is working. For example, we very often hear from our front-end tool users (schematic capture, simulation, waveform analysis) that growing design complexity is driving increased need for advanced analysis methods. Through our partnership with BDA, we offer FastSPICE and Transient Noise Analysis solutions in addition to our Tanner Spice (T-Spice) offering.

As far as back-end goes, analog layout productivity is a consistent design challenge we are working on with customers. Shortened time-to-market lead times are putting a strain on the inherent artistic (often time-consuming) nature of analog layout. Executives, CAD managers and layout engineers are struggling to balance the artistic nature of analog and the productivity requirements of the market. L-Edit – our hallmark layout editor – continues to add capabilities that tackle this design challenge head-on. This includes our analog acceleration product called HiPer DevGen – a high performance device generation tool.

The other component around layout productivity is design reuse. In the past, we had customers express frustration over the fact that designs they created on other tool flows were not easy to port to our tools. We worked hard to develop and launch our latest version – v16 – that features OpenAccess. Now users are able to open and save designs and elements within designs across different tool environments.

Another set of Tanner EDA users are focused on MEMS design. Tanner has a long history in the MEMS space, and we even have a separate business division that operates a MEMS fab for prototyping and low-volume production runs. The design challenges commonly expressed by our MEMS users are centered around the co-design of MEMS and IC devices. We’ve recently produced several webinars and a live seminar to offer best practices and design guidance to help with this manifold issue.

Q: What does Tanner EDA do?

Tanner EDA provides a complete flow for the design, layout and verification of analog and mixed-signal integrated circuits. Our tools offer just the right mix of capability and performance to provide designers a highly productive design environment. Interoperability within the EDA ecosystem has recently been bolstered with our release of L-Edit with OpenAccess.

Q: Why did you join Tanner EDA?

I was introduced to John Tanner in 2008 through our mutual participation in a Southern California business leaders organization. As I learned about Tanner EDA and their unique position in the market, I began to think about ways I could bring my own experiences and expertise to the company. Having worked in the software and services industries for much of my career, I was intimately familiar with both the challenges and opportunities Tanner EDA had given their position in the market. Since I had worked with several founders to grow their businesses and transform their business models, I also had insights into leading a division within a privately-held, founder-owned business.

When I joined, Tanner EDA was in many ways a start-up, yet the division had been in business since 1988. When I say “start-up,” I mean they were operating as a very nimble and problem-focused company. They had (and still retain) a very tight focus on the analog and mixed-signal designer. While there was great market awareness of Tanner EDA tools, it was mostly associated with the layout editor, (L-Edit), and many users had interacted with the tool five or even ten years back. There was not as much awareness around our proven commercial success. For example, Tanner EDA had been used by CSR to tape out their seminal Bluetooth chip designs, yet many people still thought of us as being a tool for universities.

Along with our investments in internal product development and other technology partnerships – with foundries and other EDA companies like BDA, Aldec, and Incentia – we’ve worked hard to improve awareness and knowledge of how robust and capable Tanner EDA tools are. I’ve enjoyed being able to draw on my skills to help engage new partners within our ecosystem and elevate the brand awareness for our company.

Q: How does Tanner EDA help with your customers’ custom IC design challenges?

Tanner EDA offers analog, mixed-signal and MEMS designers a cohesive and highly capable tool flow that provides the industry’s leading price-performance and customer support. A growing number of designers have cited issues with “Big 3” tools being bloated with features that are specific to requirements for the deep nanoscale process nodes. While our layout tool supports designers working at these nodes, our mainstay user is typically working at 90nm and above. Those users consistently cite our tools as being “just right” to help solve their design challenges efficiently and effectively, with no extraneous features getting in the way.

Operating platform is another area our users give us high marks for. Our tools run on both Windows and Linux. The ubiquitous nature of Windows-based computers and workstations aligns well with one of the principles on which John Tanner founded our company. He was intent on providing robust design tools with compelling price-performance. This shaped our direction early-on in terms of supporting Microsoft and it’s something a majority of our users continue to cite as a benefit. They like the flexibility and efficiency to upgrade PCs and maintain their Tanner EDA suites, often without a staff of dedicated CAD engineers.

Another important aspect of helping customers is technical support. We consistently hear from our users that Tanner EDA provides a level of customer support that is unrivaled in the industry. We understand that our tools are directly tied to our customers’ success in the marketplace, so we make sure that our support teams have the resources they require to ensure that success.

Q: What are the tool flows your customers are using?

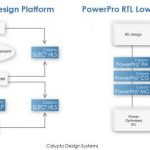

Customers who use our complete design suite are running HiPer Silicon AMS. That is our full mixed-signal solution that covers schematic capture through to tape-out.

Some customers integrate a sub-set of our design suite to build out their own solution. Our longstanding commitment to interoperability and adherence to industry standards enables users to utilize Tanner EDA tools within a hybrid flow.

We have customers using our front-end tools – incorporating our schematic capture, simulation (T-Spice and/or FastSPICE) and waveform viewer with back end tools from other vendors.

Our back-end tools can also serve as the foundation of a hybrid tool flow. Users integrate their simulator of choice with Tanner EDA’s layout editor (L-Edit) and (optionally) our physical verification products. Back-end tool integration has been greatly enhanced by our recent release of L-Edit v16 featuring OpenAccess.

Our physical verification tools are in use across a wide range of commercial applications. We have a base of users who rely exclusively on Tanner EDA for their verification needs. We also have a set of customers who use our HiPer Verify product in conjunction with other verification engines, offering a comprehensive verification solution that offers compelling price-performance.

Q: Will you be at the Design Automation Conference this year?

YES! Tanner EDA has been a long-standing exhibitor at DAC, and this year is no exception. We’ll have our own booth — #2442 – where we will be offering demonstrations of our tool suite. We will also be exhibiting in the ARM Connected Community® Pavilion. We’re again one of the sponsors of the IPL Alliance event on Tuesday night and we have a Designer Track Session on Wednesday.

Pre-registration for a demo is not required, but is strongly recommended. This link goes to our DAC2013 registration page.

Q: Where can SemiWiki readers get more information?

lang: en_US