Five or ten years ago it would have been hard to imagine someone from Ford Motors giving the keynote at a technology summit at a major EDA company like Synopsys. However, on November 2[SUP]nd[/SUP], Synopsys hosted a seminar on the topic of Automotive Architecture Design and System Testing, and Ford Technical Fellow Jim Buczkowski delivered the keynote. The other somewhat ironic side of this is that I did not drive my car to the event, preferring instead to ride light rail. Yes, traffic is that bad. We are all waiting for our autonomous cars.

What Jim had to talk about was pretty interesting. Actually the entire daylong event was captivating. Starting off with Ford first, he talked about how the Ford office in Palo Alto helps to create a culture of innovation that drives development in Dearborn. The areas he identified as relevant to the day’s topic were ADAS, powertrain, chassis and safety. Ford has created an internal initiative called One Ford to focus on their future success. The thrust of this initiative may surprise you.

Ford see four big changes in society as things that define how they need to respond as a business. The first one is urbanization. Today there are 28 mega cities with populations of over 10 million people. By 2030 it is projected that there will be 41 mega cities. These cities suffer from gridlock, which will only grow worse. It is estimated that in Paris 20% of the cars driving on the streets are looking for parking. The number of cars on the roads will overwhelm the infrastructure to support them. What’s more is that 22% of greenhouse gases come from transport, with 75% of that due to cars.

The second trend Ford sees is the growth of the global middle class. Of course the age old goal of the middle class is to own a car and their own home. We can update that goal now to include a smartphone. The phone may actually come first on the list. As we already know the phone will play a major role in transportation services.

The third big change almost goes without saying – air quality. This is an issue of increasing concern around the world. The last change is shifting consumer attitudes. Ford sees the importance of fitting into these new attitudes – and this goes beyond just providing transportation vehicles.

Generations of Americans and others around the world have seen the car as a symbol of much sought after freedom. However, due to the trends cited above, Ford now sees freedom as manifesting in the broader moniker of mobility. This is where silicon comes in – it is the enabler for giving people mobility. It is used in all forms of mobility and it is used in the information systems that will improve its efficiency and access.

So what is Ford doing to implement this strategy? If mobility is not just cars, then what is it? I was surprised to see that Ford has invested in a dynamic shuttle service called Chariot in San Francisco. It happens that Chariot was using Ford vehicles, but the main point is that Ford sees this kind of business as key to fulfilling the mobility initiative. Add to this the surprising investments in Ford GoBike and GoDrive.

Jim was quite frank during in keynote in stating that buying a car is a compromise. There are times when you want to carry cargo, and other times when you just want to transport yourself. Sometimes you want to go on the highway, or in snow, other times you just need to go 2 miles from your house to shop or to go to work. Ford sees the solution to this dilemma in the form of car sharing, fractional ownership or pay as you go. If you think about it, cars are extremely underutilized. They spend most of their lives idle in your driveway or in a parking spot.

OK, so let’s talk about where electronics comes into the picture. Jim pointed out that the design activity in cars has moved from pure mechanical and electromechanical to an era where electronics and electronic controls are enabling nearly every important vehicle system. However automotive products are situated in a very interesting position between consumer products and things like aircraft.

With a phone, it might be tolerable if some part is not working properly, but with cars – just as with airplanes – it needs to “just work.” Consumer products have high volumes and can defray development costs over large numbers of units. Airplanes are low volume and very expensive. Cars must thread the needle to find an acceptable balance with their moderate volumes, and pricing that works for automobile buyers. More so than phones, autos have regulatory requirements, but not as severe as those for aircraft.

The end goal for cars is autonomous vehicles. We are seeing cars with Level 1 and Level 2 automation. Level 1 is driver assistance, and level 2 is partial automation – like the Teslas being produced today. Though, there is some gray area regarding whether the current Tesla autopilot is Level 2 or 3. Ford feels strongly that any system that requires the driver to hand off and regain control can create ambiguity and therefore is more dangerous. Ford is skipping Level 3 and committed to having Level 4 by 2021.

Connectivity is the watchword for Ford. The car becomes another device connected to the internet. For their navigation system they will use map data as a primary data source and then overlay camera and sensor data to ascertain actual driving conditions. What this says is that they will not rely on sensor data as primary input for route decisions. Ford feels that there is still a lot of work to be done to ensure the high reliability internet connections for autos, especially at highway speeds.

They will be taking a cue from Silicon Valley in leveraging existing infrastructure as much as possible. Automobile data systems need to be secure, they want seamless cloud integration and they are looking for closer than ever cooperation with their technology partners. They see newly developed and existing standards, like ISO26262, as critical components.

The rest of the day was a deep dive into technologies that are enabling development of automotive IC’s and systems in the areas of engine control, autonomous vehicles, safety and infotainment.

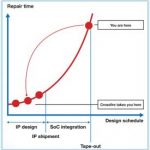

One of the big takeaways was that it is now possible to perform virtual testing of all the above systems. No longer is it necessary to hook up real hardware to test system functionality and performance. Synopsys provides tools that can be used for virtual prototyping of automotive systems. This can shorten overall development time, especially when there is hardware and software co-design. The software development can occur much sooner in the process. Also during debug, the virtual prototype can assist by providing full transparency into system state to accelerate the process of resolving issues.

Car companies are broadening their nets – witness Ford’s newer emphasis on Mobility – which will necessitate reliance on a broad selection of electronics, from power devices to advanced GPU’s. These will be integrated into complex systems to deliver what once would have been considered science fiction levels of services. The inevitable result is that car companies, their suppliers, and even the suppliers to their suppliers all need to embrace new and challenging technologies. The next 5 years will deliver some pretty amazing stuff.

For more information on the Synopsys portfolio of automotive-specific IC design tools, IP and software development tools, like those being used by the Seminar presenters, please look at the Synopsys website.

Read more SemiWiki automotive blogs here……..

Read more articles by Tom Simon here…..