Lip-Bu Tan made it very clear on his most recent call that Intel will not continue to invest in leading edge semiconductor manufacturing solo. Lip-Bu is intimately familiar with TSMC and that is the collaborative business model he envisions for Intel Foundry. I support this 100%. Intel and Samsung have tried to compete head-to-head with TSMC in the past using the IDM mentality and have failed so there is no need to keep banging one’s head against that reinforced concrete wall.

Lip-Bu Tan is clearly throwing down the gauntlet like no other Intel CEO has done before. If we want leading edge semiconductor manufacturing to continue to be developed in the United States we all need to pitch in and help. Are you listening politicians? Are you listening Apple, Qualcomm, Broadcom, Marvell, MediaTek, Amazon, Google, Microsoft, etc…

I’m not sure the media understands this. That, and the fact that Lip-Bu under promises and over delivers.

There was some pretty funny speculation after the Intel investor call. Some of which were pretty dire predictions and ridiculous comments from so called “sources”. This has all been discussed in the SemiWiki Experts Forum but let me recap:

First the absolutely most ridiculous one:

“An industry source told the publication that President Donald Trump has mandated TSMC fulfill two conditions if Taiwan is to see any tariff reduction:

- Buy a 49% stake in Intel

- Invest a further $400 billion in the US”

To be clear, TSMC investing in Intel will not help Intel. TSMC investing another $400B in the US will not help Intel. This is complete nonsense. The best comment came from my favorite analyst Stacy Rasgon (Bernstein & Co). He estimated that Intel has no more than 18 months to “land a hero customer on 14A” which I agree with completely and so does Elon Musk.

Samsung to Produce Tesla Chips in $16.5 Billion Multiyear Deal

“This is a critical point, as I will walk the line personally to accelerate the pace of progress … the fab is conveniently located not far from my house.” Elon Musk

Of course, everyone wanted to know why Intel missed this mega deal since it is exactly what Intel needs, a hero customer. Personally, I think it is a huge distraction having Elon Musk intimately involved in your business which could end tragically. That is not a risk I would take as the CEO of Intel unless it was THE absolute last resort, which it probably is for Samsung Foundry. Samsung also has plenty of other things to sell Tesla (Memory, Display Tech, Sensors, etc…) so this is a better fit than TSMC or Intel Foundry.

I do hope this deal is successful for all. The foundry race needs three fast horses. The semiconductor industry thrives on innovation and innovation thrives when there is competition, absolutely.

On the positive side of this mega announcement, hopefully other companies will step up and make similar multi-billion-dollar partnerships with Intel Foundry if only to butt egos with Elon Musk. Are you listening Jeff Bezos? How about investing in the industry that helped you afford a $500M yacht? The same for Bill Gates, where would Microsoft be without Intel? How about you Mark Zuckerberg? Where would we all be without leading edge semiconductor manufacturing? And where will we be without access to it in the future because that could certainly happen.

If we want the US to continue to lead semiconductor manufacturing like we have for the past 70+ years we need support from politicians, billionaires, the top fabless semiconductor companies, and most certainly Intel employees.

What should Intel executives do? Simple, just follow Lip-Bu’s leadership and be transparent, play the cards you are dealt, deliver on your commitments, and make Intel great again. Just my opinion of course.

Just a final comment on the most recent CEO turmoil:

Lip-Bu Tan is known all over the world. He was on the Intel Board of Directors before becoming CEO so the Intel Board certainly knows him. The CEO offer letter specifically allowed Lip-Bu to continue his work with Walden International. Lip-Bu founded Walden 38 years ago and it is no secret as to what they do. Walden has invested in hundreds of companies around the world, and yes some of them are in China, but the majority are here in the United States.

What happens next? It will be interesting to see if the semiconductor industry allows political interference in choosing our leadership. Hopefully that is not the case because if it is we are in for a very bumpy ride. Intel has no cause to remove Lip-Bu Tan so if there is a separation it will be on Lip-Bu’s terms. I for one hope that is not the case.

My commitment to you and our company. A message from Intel CEO Lip-Bu Tan to all company employees.

The following note from Lip-Bu Tan was sent to all Intel Corporation employees on August 7, 2025:

Dear Team,

I know there has been a lot in the news today, and I want to take a moment to address it directly with you.

Let me start by saying this: The United States has been my home for more than 40 years. I love this country and am profoundly grateful for the opportunities it has given me. I also love this company. Leading Intel at this critical moment is not just a job – it’s a privilege. This industry has given me so much, our company has played such a pivotal role, and it’s the honor of my career to work with you all to restore Intel’s strength and create the innovations of the future. Intel’s success is essential to U.S. technology and manufacturing leadership, national security, and economic strength. This is what fuels our business around the world. It’s what motivated me to join this team, and it’s what drives me every day to advance the important work we’re doing together to build a stronger future.

There has been a lot of misinformation circulating about my past roles at Walden International and Cadence Design Systems. I want to be absolutely clear: Over 40+ years in the industry, I’ve built relationships around the world and across our diverse ecosystem – and I have always operated within the highest legal and ethical standards. My reputation has been built on trust – on doing what I say I’ll do, and doing it the right way. This is the same way I am leading Intel.

We are engaging with the Administration to address the matters that have been raised and ensure they have the facts. I fully share the President’s commitment to advancing U.S. national and economic security, I appreciate his leadership to advance these priorities, and I’m proud to lead a company that is so central to these goals.

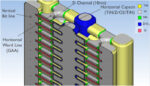

The Board is fully supportive of the work we are doing to transform our company, innovate for our customers, and execute with discipline – and we are making progress. It’s especially exciting to see us ramping toward high-volume manufacturing using the most advanced semiconductor process technology in the country later this year. It will be a major milestone that’s a testament to your work and the important role Intel plays in the U.S. technology ecosystem.

Looking ahead, our mission is clear, and our opportunity is enormous. I’m proud to be on this journey with you.

Thank you for everything you’re doing to strengthen our company for the future.

Lip-Bu

https://newsroom.intel.com/corporate/my-commitment-to-you-and-our-company

Also Read:

Why I Think Intel 3.0 Will Succeed