Wow! We always hear semiconductor companies complain about the lack of innovation amongst the EDA leaders. Placing high on the Deloitte 500 list shows that innovation is alive and well in EDA and it IS possible to have a meaningful impact regardless of your overall size. It is worth noting that there are very few EDA companies that have ever won this award.

The Deloitte’s 2011 Technology Fast 500™ is a ranking of the 500 fastest growing technology, media, telecommunications, life sciences and clean technology companies in North America. The winners are selected based on percentage fiscal year revenue growth from 2006 to 2010. During this period, Berkeley Design Automation’s revenue grew 787%, while its customer base grew to over 110 semiconductor companies worldwide.

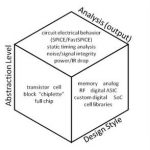

There are more and more pain points cropping up as our customers try to close the gap between circuit design and actual silicon performance at ever-shrinking process nodes. Physics and statistics are becoming critical to understand electronics. The focus at BDA is on those problems that arise when analog, mixed-signal, RF, and custom digital circuit content grows rapidly. Technology that is directly targeted to solve these pain points, together with knowledgeable application expertise, timely responsiveness to customer issues, and the right business models are the key ingredients behind the company’s rapid revenue growth.

It is an incredible honor for BDA to win this prestigious award. It validates their mission, strategy, and execution in solving some of the newest and most difficult problems for semiconductor design teams. BDA is widely recognized for its technology leadership via its Analog FastSPICE™ Platform and its growing market share in the electronic design automation industry. Berkeley Design Automation is the only EDA company selected for this year’s ranking.

Ravi Subramanian, Berkeley Design Automation’s chief executive officer, credits the company’s incredible revenue growth on the combination of the:

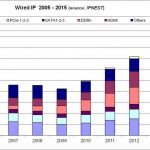

- Industry’s rapid move to nanometer mixed-signal design starts

- Company’s breakthrough verification technology

- Collaboration with key customers and partners

- Widespread customer success with this new technology

“This is a prestigious honor for Berkeley Design Automation, and we would like to share this honor with our customers. Our stellar team, strong technology base, innovative products, outstanding customer focus, and execution discipline have helped ensure our strong and consistent year-on-year revenue growth, even as we faced challenging economic times. I would like to thank our customers for fueling this growth via the strong demand for our products.”

Berkeley Design Automation, Inc. is the recognized leader in nanometer circuit verification. The company combines the world’s fastest nanometer circuit verification platform, Analog FastSPICE, with exceptional application expertise to uniquely address nanometer circuit design challenges. More than 100 companies rely on Berkeley Design Automation to verify their nanometer-scale circuits. Berkeley Design Automation has received numerous industry awards and is widely recognized for its technology leadership and contributions to the electronics industry. The company is privately held and backed by Woodside Fund, Bessemer Venture Partners, Panasonic Corp., NTT Corp., IT-Farm, and MUFJ Capital.

For more information, visit the BDA landing page on SemiWiki:

http://www.semiwiki.com/forum/content/section/256-berkeley-design.html