BYOD – bring your own device – has swept enterprises like a firestorm as CEOs wonder why they can’t use their shiny new iPad on the corporate network, and send their IT guys and gals off to make it happen. Under the right conditions and informed use, BYOD can be a productivity boom and not mess security and privacy up too badly for many apps.

[COMMENT] Continue reading “DARPA looking for new base stations in new BYOD game”

Words of AMS Wisdom from the Developer of Spectre, Spectre RF, Verilog-A, Verilog-AMS

Ken Kundert while at Cadence developed: Spectre, Spectre RF, Verilog-A and Verilog-AMS. About 6 years ago he and Henry Chang left Cadence and created a consulting company called The Designers Guide.

Continue reading “Words of AMS Wisdom from the Developer of Spectre, Spectre RF, Verilog-A, Verilog-AMS”

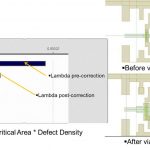

DFM Provides Proven Value

Although design for manufacturing (DFM) tools and techniques have been around for several nodes, a lot of designers remain skeptical about their actual value, especially since many products still make it successfully to market without the use of DFM.

Continue reading “DFM Provides Proven Value”

Power to the Drones

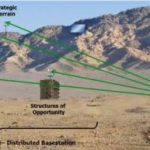

Unmanned systems are becoming indispensable to military forces and are used across all of land, sea and air. The generic name for such unmanned systems is UXS, usually UAS (air), UGS (ground) or UUS (underwater). The UAS is the most visible, both due to military strikes and the views of Japan after the Tsunami when areas were unreachable by other means.

As the value of UXS continues to be proven in the field, there is a drive towards lower-cost and lower-risk platforms. But as the systems get smaller but require greater capability (smart weapons, electronic counter-measures, embedded intelligence) the demand for power is potentially insatiable. Especially for airborne vehicles, there is an obvious balance between the amount of sustained power and the weight of power generation and storage systems (this doesn’t sound all that different from the same types of tradeoffs that smartphone designers need to make).

One of the promises of the ANSYS acquisition of Apache is that it become possible to combine the physics-based simulation tools with electronic system modeling to create virtual representations of vehicles and payloads and analyze space, power, thermal prior to physical testing (prior to even building the vehicle).

Power management must be addressed early in the design phase, at the architectural level, to ensure a long-enduring unit. Two of the smallest unmanned air systems currently in operation rely solely on batteries to power their motors and on-board electronic systems. Both the WASP III and Raven micro air vehicles (MAVS) can fly for approximately 45 minutes to 1 hour before they need to land and recharge their batteries. Reducing power consumption in these designs, therefore, is critical to the ability to deliver real-time surveillance information.

But these MAVs carry the same amount of on-board cameras and surveillance capabilities as larger, high-end UASs. Unnecessary power consumption of UAS chips will lead not only to early depletion of their battery power sources, but to electrical and thermal reliability issues, which can shorten the UAS’s expected lifetime and render it unreliable in the field. Military equipment operates, almost by definition, in a hostile environment and reliability in extreme environmental conditions, especially electromagnetic interference, is obviously of paramount importance.

Next-generation unmanned systems are being developed to meet growing requirements of field reconnaissance, strike capability and longer mission duration, as well as new fields of operation in land, sea and air. As the military seeks to expand the role of unmanned systems, industry must rise to the urgent challenge of ensuring that power supply requirements of these systems are met within their allotted power and thermal envelope. Only a multiphysics approach, initiated early in the design phase, can simulate the power consumption and thermal dissipation of these complex systems, enabling successful power reduction and thermal cooling solutions for onboard electronics. The power integrity of these systems and their ability to conform to reliability and emissions standards can be validated through ANSYS and Apache simulation solutions for the individual components as well as for comprehensive onboard electronic systems.

Read the white-paper by Robert Harwood of ANSYS and Margaret Schmitt of Apache here.

Apple’s iPAD 3 Kicks Off a Season For Silicon Valley Re-Alignments

The Corporate PC may finally be on life supports and with it the purveyors of the hardware and software solutions as consumer adoption of new technology outpaces the carefully planned IT budgets that guarantee positive 3 year Returns on Investments (ROI). The Apple of the consumer’s eye will soon feast on the iPAD 3 with its retina display and 4G LTE that untethers the productivity class for good from centralized IT departments. It’s “Ash Heap of History Time.”

If it were just the iPAD3 that was rolling out, you could push back and say, Please! However, quick to follow will be redesigned MAC Air’s and MAC Book Pro’s that will feature Intel Ivy Bridge processors and 4G LTE as well. Then the IT department has to admit that the “Cloud” is everywhere and that it no longer makes sense to deal with all the complexity of software versions and updates between the various versions of Dell and HP PCs.

The pain will soon start to get extreme for Microsoft and Google as the train that left the station years ago in terms of the mobile hardware that rests in the users hands on a 24/7 basis will be available from just one vendor: Apple. A sign that chaos reigns is when those on the defense start coming up with half answers. For example, Microsoft is rumored to be working on a version of Office for iOS. That’s nice and what is the price? Surely much less than a version delivered on a Microsoft Cloud. By relying on Nokia and Apple to deliver the hardware, Microsoft falls into a two degrees of separation gap from the end customer. Meanwhile Intel ships Xeon’s at ever increasing prices to Microsoft’s data center and to those of Google and Facebook. The Intel bacteria have glommed onto the Data Center Host.

Is the Motorola alliance with Intel for Smartphones an all encompassing one that precludes the use of nVidia or Qualcomm. What about tablet and Ultrabooks? When will Google/Motorola wake up and see that their main revenue stream of search can be redirected by Siri to the iCloud? Time to consider Andy Grove’s dictum: “Only the Paranoid Survive.”

It is truly historical to observe the alliances that are breaking under the duress of Apple’s assault and the resulting ones to form as a means to stop the blitzkrieg. Intel’s client price and delivery model now revolves around the Apple MAC Air. The pricing every other OEM gets has to be higher than Apple’s. And so, every other OEM and partner is a 2[SUP]nd[/SUP] class citizen sitting at the back of the bus. Apple data centers will receive favorable Xeon treatment. However, what if Google went to Intel and promised to up the server buy while also planning to build 10M tablets a quarter based on Atom. Intel would need to consider a front of the bus seat unless Apple A6 is already taped-out in 22nm.

An Intel no bid to Google then leads to the next scenario – a Google/AMD joint venture on x86 Server Processors and possibly a low cost x86 mobile processor for ultrabooks, so that the search bar remains “Google”. The same scenario could play out for Microsoft and AMD. This is what will make the semiconductor industry extremely interesting over the next several years.

On the semiconductor side, Qualcomm has to consider scaling dramatically in 2012 as they leverage their 4G advantage. Paul Otellini, Intel’s CEO claimed in the last earnings conference call that the communications silicon is being pulled into the x86 platform. In one way or another, Intel is forcing Qualcomm to retreat into an IP mode or to man up in a Jerry Sanders fashion. Furthermore, Qualcomm has to realize that if Intel seeks to own Ultrabook down through tablets to the smartphones then Qualcomm has to make a maximum thrust into the ultrabook space and it can’t be with just ARM. A Qualcomm – AMD “x86 Snapdragon” would allow them to increase the penetration of the communications content just as the x86 value piece is waning. In reality the x86 and ARM cores are both diminishing as a percentage of the overall mobile platform.

We live not only in interesting times but one that is about to have incredible amounts of upheaval. Not all of the Paranoid will Survive.

FULL DISCLOSURE: I am long AAPL, INTC, QCOM, ALTR

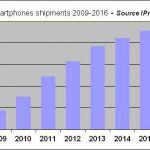

Smartphone shipments in Q4’11, the Milky Way the new limit!

In a previous blog, I was forecasting smartphone shipment to reach 430 million units in 2011. I was wrong! Apparently, I am not better than other analysts, as the actual figures for the smartphone shipment in 2011 are more than slightly different, as these have topped 491.4 million units! After 304 million in 2010, that’s a 61.3 percent year over year increase, according with IDC. IPNEST has revised the smartphone shipments forecast for 2012- 2016, taking into account these latest figures for 2011: we expect almost 1 billion smartphoneto be shipped in 2016.

If we come back to the actual shipments, in 2011 one out of three wirelesses handset shipped was a smartphone. This is to be compared with 2010, when it was one out of five. What is the impact on our day to day business, IP and Semiconductor?

Application processor market: this is the obvious first segment to look at, even if it’s not the only one. With an Average Selling Price (ASP) in the $20 range in 2011 for an application processor dedicated to smartphone, this segment has represented a $10 billion market in 2011. If we look at the Total Addressable Market (TAM), it is slightly smaller… this is an understatement, as the difference between the total market and the TAM is made of the A5 (A4) shipments. Apple shipping application processor to… Apple. As Apple has shipped about 60 million iPhone during 2011, the application processor TAM is equal to (490 -60)*20 or $8.6 billion, or almost 3% of the total SC market of $300 billion.

PMIC market: those who have read my previous post about the Power Management IC market have discovered like I did that this segment, even if it’s not as impressive as application processor, is generating pretty decent sales, as the PMIC content has been evaluated around $8 by smartphone (and $20 by Media Tablet!). The PMIC market in the smartphone segment only can be evaluated at $4 billion. If we add the Media Tablet segment, with 63 million units shipped in 2011 according with IDC, we add $1.26 billion to the PMIC segment. Thus, for the smartphone and Media Tablet segment, the PMIC TAM was above $5 billionin 2011. Pretty impressive for a SC segment almost neglected by the IDC, Gartner et al., as they focus on the more sexy application processor segment!

MIPI IP: IPNEST analysis is that MIPI, as any emerging technologies, is firstly used in the high end market, or smartphone segment. As with any new technology, integrating one of the MIPI specifications (CSI, DSI, DigRF, UniPro, LLI and more, see MIPI organization websitefor more information) represent an investment to make, in order to understand the specification, design the function or acquire the IP externally, integrate it into the IC (it can be the application processor or one of the many peripheral IC), and so on… But the many advantages generated by MIPI usage will certainly bring a high return on this investment, especially to the system integrator (manufacturing the smartphone) and ultimately to the end user, as MIPI allow for:

- Lower power consumption compared with other interfaces

- Standardization in the way to interface the various peripheral devices with the application processor, like camera controller or display controller IC for example, allowing to build the complete system in an easier way, thanks to the guaranteed compatibility between IC compliant with the same interface specification.

If the smartphone shipments are rocketing, that should be good for MIPI adoption, as more than expected MIPI powered IC will be manufactured. Then, when the production volumes are growing, it’s usual to see the IC price going down. When the price is going down, the over-cost associated with the integration of a new technology tend to disappear. It’s a kind of virtuous cycle: more smartphone shipped means more MIPI powered IC manufactured at a more affordable price for the customer, then more customers supporting the technology. Look at Qualcomm: a couple of years ago, the company was not supporting MIPI (but MDDI, a homemade concurrent specification). Now, Qualcomm has dropped MDDI and fully support MIPI!

For more exaustive information about MIPI, see MIPI Orgor “MIPI IP Survey“

By Eric Estevefrom IPnest

AMD Financials are Puzzling!?!?!?!

As I mentioned in my previous blog, AMD and GlobalFoundries,it is rather difficult to interpret AMD’s financial results. At the end of the quarterly earnings conference calls analysts get to ask questions. It is the comedy relief portion of the call usually, so I blog this today to better prepare these so called analysts for their job of helping investors understand what is really going on insideAMD.

Continue reading “AMD Financials are Puzzling!?!?!?!”

DFM Industry Survey

As part of the DFM Conference at the SPIE Advance Lithography symposium, the DFM committee is conducting an informal survey on the current state of Design For Manufacturability in the Semiconductor Industry.

Please take this anonymous 16 question survey to identify critical Design for Manufacturability (DFM) issues facing the semiconductor industry.

Yes, there is such a thing as a free…model

I have been saying for years, ever since I started working at VaST, the biggest barrier to adoption of virtual platform technology for what I like to call virtualized software development is the availability of models. If models do not already exist when they are needed there are two issues: it takes money to develop them but, probably more importantly, it takes time. Since a large part of the attraction of virtual platforms is that they can potentially be available before reference boards, chips, real cell-phones etc, anything that soaks up that time makes the approach less attractive. A month developing models is a month slip in the software development schedule.

There have been a number of attempts to address this problem, the most serious of which is Synopsys’s TLMCentral. When this started last year, it was focused on being a central location to find models that were commercially available either through the site, or, more often, elsewhere. There are now over 800 such models available.

This year they are adding a push to encourage model developers to upload open-source models. Obviously nobody will do this for something proprietary like a processor, nor something expensive to develop that therefore can easily be sold. But there is really little downside to sharing a model for a UART or a timer, and there is little point in every company developing their own generic timer model.

To encourage people to get started, Synopsys have uploaded 16 or so models that can be freely downloaded. Some have already been downloaded 30 times so there is definitely demand there. These are open-source models with no licensing fees.

And as a more direct form of encouragement there are several competitions to win an iPad2 (and I’m sure they’ll switch it to iPad3 if Apple announce a new one as some people expect).

- submit any model. One of the first 50 submitted will win (although confusingly the front page of TLMCentral says upload the 50th model and win; maybe you win another one for that too)

- be the person who uploads the most models by the end of March

- upload the model that gets the highest vote by end of April

- upload the model that gets the most downloads by the end of May

- or upload a model of a sensor interface such as accelerometer, gyroscope, magnetometer or proximity sensor (deadline February 17th)

Of course there are some conditions, the models need to be written in System-C TLM 2.0 being the main one.

More details about all of this, including the competitions, here.

DFM at SPIE Advance Litho show

This year’s SPIE Advanced Lithography is loaded with interesting keynotes and sessions. To help me narrow down what to see, I spoke with John Sturtevant. John is co-chair of the Design for Manufacturability through Design-Process Integration conference, and the director for technical marketing for RET products at Mentor Graphics.

San Jose Convention Center

All the cool kids will be there

I asked him how it’s changed since first introduced six years ago. John has been co-chair of the DFM conference for the last five years, so he has perspective. Here’s what he told me.

The conference saw a steady upsurge in number of papers in years 1-4, reflecting to a certain extent the hype that was DFM early on, as startups appeared on the scene, and “DFx” appeared on the business cards of an increasing number of engineers and VPs. As we separated the wheat from the chaff, most startups disappeared, and SPIE paper submissions to the conference dropped off somewhat to a steady state of around 40 papers. This was consistent with the predictions of Joe Sawicki in his invited paper in 2004, the second year of the conference.

The wheat which is left now grows in the fields of

-

[*=1]Multi-patterning implications to design and manufacturing

[*=1]Implications of EUV

[*=1]Design variability effects in manufacturing

[*=1]Litho-friendly design

[*=1]Restricted design rules

John recommends these papers in the DFM conference at SPIE:

Wednesday 10:40a, “Layout optimization through robust pattern learning and prediction in SADP gridded designs.” UC Santa Barbara and Mentor researchers present their study of placement-level optimization, including how to build a predictive model for layout pattern classification, and applying the model to find and eliminate printing hotspots. [8327-04]

Wednesday 1:50p, “Fully integrated litho aware PnR design solution.” STMicroelectronics and Mentor engineers present the STMicroelectronics back-end CAD solution for litho hotspot search and repair that is based on pattern matching and local re-route abilities in place and route tools. [8327-09]

Wednesday 2:30p, “Smart double-cut via insertion flow with dynamic design-rules compliance for fast new technology adoption.” Mentor and GLOBALFOUNDRIES engineers introduce an automatic redundant-via insertion flow. [8327-11]

Thursday 1:40p,“Thickness-aware LFD for the hotspot detection induced by topology.” Samsung and Mentor engineers present a method for advanced process window simulations with awareness of chip. [8327-24]

Thursday 2:00p, “The complexity of fill at 28nm and beyond.” Mentor and AMD engineers discuss modern fill challenges and advances in technology for 28nm. [8327-25]

And, if you’re interested to see how triple patterning will work for 14nm designs, go see “14nm M1 triple patterning”at 5:10p on Wednesday. [8326-38]