Next Wednesday is the Common Platform Technology Forum. “Common Platform” is a name that only a committee could have come up with, giving no clue as to what it actually is. As you probably know, there are various process clubs sharing the costs of technology development (TD) and one of them consists of IBM, Samsung and Global Foundries. Although they have many partners, historically they have worked closely with ARM and Synopsys.

TD versus capital has gone through a couple of phases. It used to be that anyone could build a fab but getting a process to run in it was expensive. Then in the 90s, fabs suddenly became really expensive and the cost of licensing a process was a lot less. But then TD got really hard again, and it became so expensive that only Intel could really afford to go it completely alone. Hence alliances like the Common Platform.

Wednesday March 14th at the Santa Clara Convention Center is this years Common Platform Technology Forum. The keynote speakers (from 9am to 11.30am) are:

- Dr. Gary Patton, Vice President of Semiconductor Research & Development Center, IBM

- Gregg Bartlett, Chief Technology Officer, GLOBALFOUNDRIES

- Dr. Jong Shik Yoon, Senior Vice President of Semiconductor R&D, Samsung

- Simon Segars, Executive Vice President and General Manager, Physical IP Division, ARM

There is a partner pavilion then open for the rest of the day. I’m presuming lunch is provided there too. And since it is Pi day (3.14), from 1.30pm they will be serving…wait for it…specialty pies.

From 1-2pm is a panel session on the R&D pipeline for future technology innovation. There are representatives of (surprise) Global Foundries, Samsung and IBM. Along with ARM and the College of Nanoscale Science and Engineering (which I confess to never having heard of).

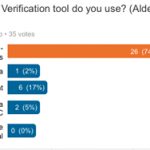

In the afternoon are presentations from Synopsys, Cadence and Mentor (how’s that for EDA neutrality?).

At 2pm, John Chilton of Synopsys talks about designing ARM-based SoCs at 28nm and 20nm. He is followed, at 3pm, by Sampta Bansal of Cadence, who sees Synopsys’s 20nm and raises it by talking about delivering on 20nm and embarking on 14nm. Then, at 4pm, Mentor’s Michael White talks about double patterning at 20nm.

For me the Mentor presentation looks the most interesting since it looks like a sort of introduction to double patterning, a subject that I need to learn a lot more about. And so, probably, do you. To register click on the banner below.