FPGA-based prototype boards are a fast, cost-effective platform for SoC system validation but they are notoriously difficult to set up and to debug. There is a big upside, however, allowing early software integration and testing and thus finding bugs in both the software and the SoC earlier. This approach is much cheaper than commercial emulators. However, problems of debug visibility and the need for repeated slow FPGA compiles limits their use to late in the design cycle.

FPGA-based prototype boards are a fast, cost-effective platform for SoC system validation but they are notoriously difficult to set up and to debug. There is a big upside, however, allowing early software integration and testing and thus finding bugs in both the software and the SoC earlier. This approach is much cheaper than commercial emulators. However, problems of debug visibility and the need for repeated slow FPGA compiles limits their use to late in the design cycle.

The basic problem is that you need to decide in advance which signals to monitor, and add code to the RTL to bring those signals out. Of course, they always turn out to be the wrong set of signals, but to make a change requires adding the new signals and recompiling the whole FPGA. The number of pins available also restricts how many signals can be probed.

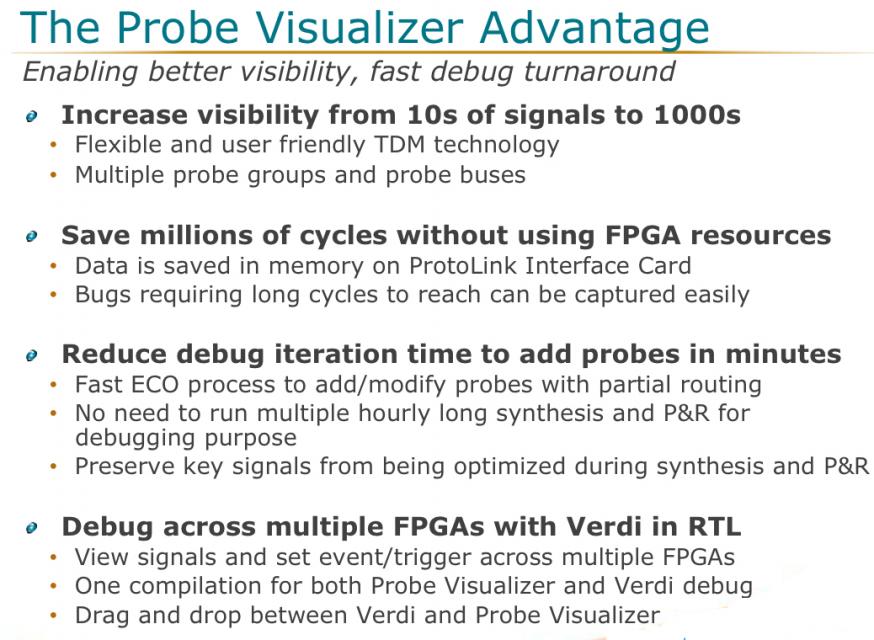

What you would really like is to be able to have thousands of signals probed, and be able to change your mind to add new probes without requiring a complete recompile of the FPGA which can take hours.

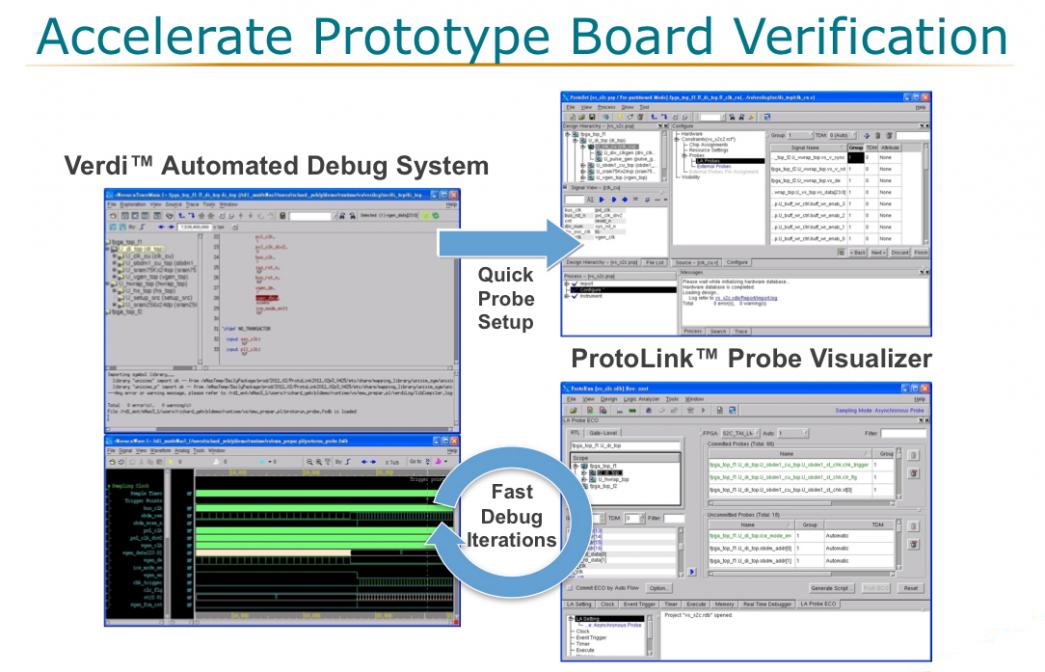

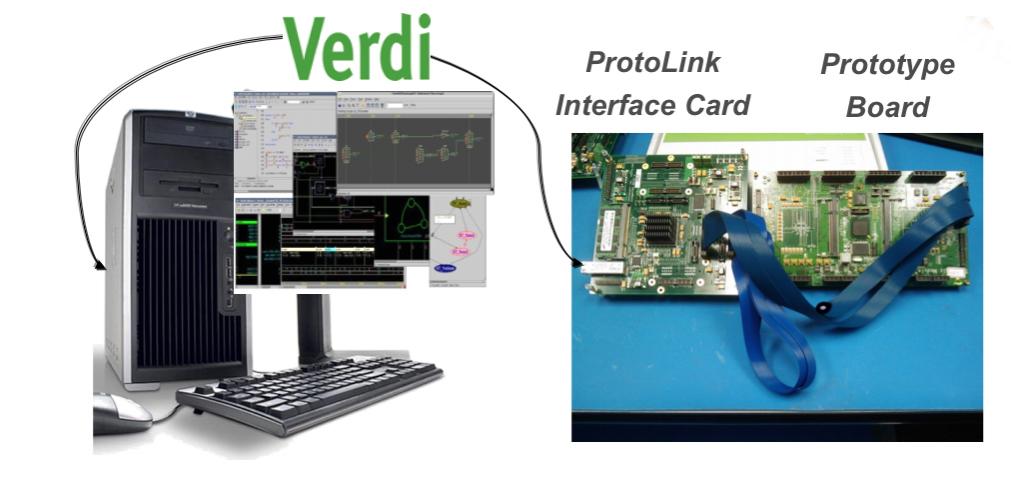

Protolink proble visualizer is a mixture of hardware and some clever software that gives just this capability. The way it works is that the RTL for the design is augmented with a bit of code before compilation (there is an overhead of a few percent for this). After compilation, the detailed routing of the FPGA is analyzed, the dummy module is replaced with the actual gates required for Protolink and then the verification can be run with the ProtoLink interface card attached to the prototype board. If an additional signal needs to be probed then small adjustments to the FPGA are all that are required.

The traditional approach gives the capability to monitor tens of signals for a limited number of cycles, and with the time required to add a new signal measured in hours or even days. With Prove Visuallizer it is possible to monitor thousands of signals for millions of cycles, and adding a new signal to probe is a matter of minutes.

The traditional approach gives the capability to monitor tens of signals for a limited number of cycles, and with the time required to add a new signal measured in hours or even days. With Prove Visuallizer it is possible to monitor thousands of signals for millions of cycles, and adding a new signal to probe is a matter of minutes.

The whole system is interfaced through Verdi, giving a common user-interface for simulation, FPGA prototyping and conventional in-circuit emulation. Verdi’s advanced visualization, tracing and analysis all operate to produce an extremely productive test and debug environment.

Probe Visuallizer backgrounder

Share this post via:

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?