We have seen last week in a first post how crucial was the IP qualification process (TSMC 9000) to increase the probability of successfully Tape Out a chip. Being able to discriminate between dangerous and safe IP is the first step of TSMC 9000 Quality process, IP tagging is the complementary step, almost as essential as the first one. That’s why, for every IP or Library going through TSMC 9000, an unique IP tag is created and inserted into its GDSII stream for identification.

IP tagging is supported by using VSIA standard specification, which can be found here

The IP Tag allows carrying the IP vendor information and IP denomination, and also all the quality information and production status of the specific IP or Library. When TSMC customer tapes out a chip, the GDSII data base will include for every IP the physical information used to generate masks, as usual, and also the information previously included in the tag (Vendor name, IP denomination, TSMC 9000 qualification process results, production status, etc.). Any designer who has participated in the tape-out phase knows that during these crazy days, where everybody is working under heavy stress, it sometimes happens that, for example, a wrong IP version can be used instead of the right one. TSMC IP tagging policy, linked with TSMC 9000 qualification process, will ensure that such a wrong IP will NOT pass through and lead to a “fatal” error, or failed prototypes.

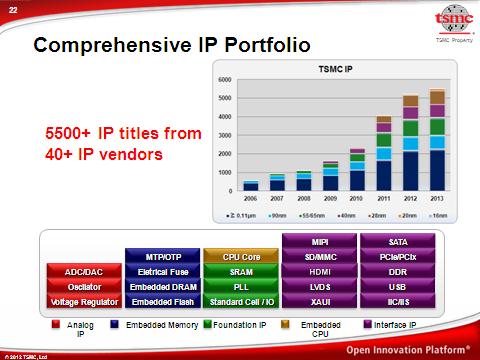

Including soft-IP partners, TSMC IP Alliance counts more than 40 IP vendors (you can see the various company logos above). But what’s happen if you integrate an IP from a vendor not part of IP Alliance Partners? Does this necessarily mean that your design will not benefit from TSMC IP tagging? For the first time, TSMC enables “open access” to its TSMC9000 IP tagging “specification“, and non-IP Alliance members and IP industry can now have full access to the IP tagging specification, thus enjoy the full benefits of the program. As far as the vendor you have sourced the IP from decides to use the IP tagging (supported by using VSIA standard specification), your GDSII chip description can now completely support IP tagging!

IP vendors being part of the TSMC IP Alliance are supporting a total of 5500+ IP titles: remember that that mean that each of these IP have passed TSMC 9000 Qualification process. On the other hand, semiconductor is a fast moving industry, we see new protocols or mixed-signal functions emerging every year, and new IP vendor offering innovative products emerging, not yet being part of the TSMC IP Alliance just because joining the Alliance is a process which take time. With the IP tagging contribution (“TSMC9000 IP tag specification”), TSMC extends its Open Innovation Platform® (OIP) ecosystem to non-IP Alliance members, for the final benefit of the common customers.

For these IP vendors not yet part of the IP Alliance, accessing to TSMC IP tag specification can be a good way to build up quality/production track records within TSMC (OIP).

As a remark, the TSMC9000 IP Tag specification can be freely downloaded from:

http://www.tsmc.com/english/dedicatedFoundry/services/tsmc9000_iptag.htm

and the associated IP Tag utility will be provided upon request.

It will enables customers to have full visibility into the vendor IP’s quality and production status and from a market positioning point of view, enables the vendor to be on a faster track to become IP Alliance member. In other words, accessing “TSMC9000 IP Tag specification” program, is not only good for an IP vendor customers, but it’s also a good way to faster join TSMC IP Alliance, which in turn is certainly good for developing business!

Share this post via:

Solving the EDA tool fragmentation crisis