While the debate rages on about 28nm yield at foundry juggernaut TSMC, on Monday I attended a webinar on 20nm IC design hosted by TSMC and Synopsys. Double Patterning Technology (DPT) becomes a requirement for several layers of your 20nm IC design which then impact many of your EDA tools and methodology.… Read More

Tag: webinar

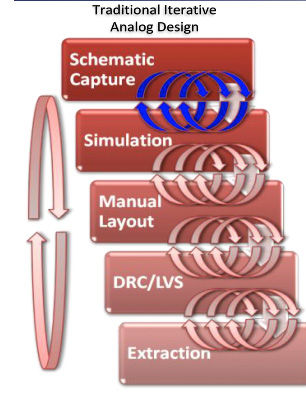

Analog Circuit Optimization

Gim Tan at Magma did a webinar on analog circuit optimization, so I watched it today to see what I could learn about their approach. Gim is a Staff AE, so not much marketing fluff to wade through in this webinar.

The old way of designing custom analog circuits involves many tedious and error prone iterations between front-end (Schematic… Read More

MEMS and IC Co-design

This morning I attended a webinar about MEMS and IC co-design from a company called SoftMEMS along with Tanner EDA. I learned that you can co-design MEMS and IC either in a bottom-up or top-down methodology, and that this particular flow has import/export options to fit in with your mechanical simulation tools (Ansys, Comsol, Open… Read More

How Co-design of MEMS-IC Saves Time

I learned about MEMS layout automation at a webinar in December and plan to attend another webinar next week on April 10thwhere two companies have created a MEMS-IC co-design flow, Tanner EDA and SoftMEMS. The big challenge is to ensure that the MEMS and electronic parts of a new design will simulate correctly before committing … Read More

Power Issues for Chip and Board: webinar

Last month Brian Bailey at EDN moderated an interesting webinar about power issues. Unusually, it combined two different domains: doing things by modeling and actually taking measurements off real chips and boards. The two participants were Arvind Shanmugavel from the Apache subsidiary of Ansys, and Randy White from Tektronix.… Read More

Custom Processors: Webinar

What is a custom processor? Or Application Specific Instruction-set Processor (ASIP) which is the buzzword which may or may not catch on.

Most programming is done on a processor with a fixed instruction set: think Intel x86 or ARM. Intel or ARM decided on what instructions to include, based on a lot of benchmarking across a wide range… Read More

MEMS layout and automation

At a webinar today I listened and learned about how a tool called L-Edit can be used to layout MEMS designs plus automate the task to be more productive. I can see how the history of IC layout editing is now being repeated with MEMS because in the earliest IC layout tools we could only do manual entry of polygons, then gradually we got cells… Read More

Low Power Webinar Series

At DAC 2011 in San Diego, Apache gave many product presentations. Of course not everyone could make DAC or could make all the presentations in which they were interested. So from mid-July until mid-August these presentations will be given as webinars. Details, and links for registration, are here on the Apache website.

The seminars… Read More