Signal Integrity (SI) and Power Integrity (PI) issues are critical to analyze, ensuring the proper operation of PCB systems and IC packages, yet the computational demands from EDA tools can cause engineers to only analyze what they deem are critical signals, instead of the entire system. Cadence has managed to overcome this SI/PI… Read More

Tag: voltus

EDA Flows for 3D Die Integration

Background

The emergence of 2.5D heterogeneous die integration using a silicon (or organic) interposer has enabled unique system architectures. The term “More than Moore” has been used to describe the circuit density and cost advantages of leveraging multiple die in the package, the die potentially in different process technologies. … Read More

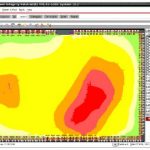

TECHTALK: Hierarchical PI Analysis of Large Designs with Voltus Solution

Power integrity analysis in large chip designs is especially challenging thanks to the huge dynamic range the analysis must span. At one end, EM estimation and IR drop through interconnect and advanced transistor structures require circuit-level insight—very fine-grained insight but across a huge design. At the other, activity… Read More

Cadence Defines a New Signoff Paradigm with Tempus PI

Semiconductor technology advances have a way of rewriting the rule book. As process geometries shrink, subtle effects graduate to mainstream problems. Performance curves can become inverted. And no matter what else occurs, low power demands are constantly reducing voltage and design margins along with it. Sometimes these… Read More

A True Signoff for 7nm and Beyond

The Tale of Three Metrics

Meeting PPA (Performance, Power and Area) target is key to a successful design tapeout. These mainstream QoR (Quality of Results) metrics are rather empirical yet inter-correlated and have been expanded to be linked with other metrics such as yield, cost and reliability. While the recent CPU performance… Read More

A New Unified Power Solution at All Levels

When situation demands, multiple solutions appear with a slight lag of time. Similar is the story with estimating and optimizing power at SoC level. In the SoC era, power has become a critical criterion long ago, and there are tools available for power analysis and optimization. However, with more mobile and IoT (Internet of Things)… Read More

Innovus: Cadence’s Next Generation Implementation System

Yesterday was the first day of CDNLive. There were three keynotes. The first was by Lip-Bu Tan, Cadence’s CEO (and the Chairman of Walden International that he will be the first to remind you). The most interesting tidbit was that Cadence now has over 1000 people working on IP and that it represents 11% of their revenue. Then… Read More

Cadence Completes Power Signoff Solution with Voltus-Fi

You probably remember Cadence introduced Voltus towards the end of last year at their signoff summit. This was aimed at digital designers. Prior to that they had announced Tempus, their static timing analysis tool. More recently they announced Quantus QRC extraction. All of these tools that end in -us have been re-architected… Read More

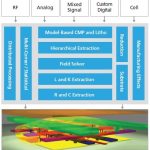

A Deeper Insight into Quantus QRC Extraction Solution

Last month Cadenceannounced its fastest parasitic extraction tool (minimum 5 times better performance compared to other available tools) which can handle growing design sizes with interconnect explosion, number of parasitics and complexities at advanced process nodes including FinFETs, without impacting accuracy of … Read More

Signoff Summit and Voltus

Yesterday Cadence had an all-day Signoff Summit where they talked about the tools that they have for signoff in advanced nodes. Well, of course, those tools work just fine in non-advanced nodes too, but at 20nm and 16nm there are FinFETs, double patterning, timing impacts from dummy metal fill, a gazillion corners to be analyzed… Read More