You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

This article about verification is part 2 of a two article series. Please see part 1 on validation HERE.

Verification is a field that has emerged as its own discipline. It’s no longer being relegated to an activity led by the design team to which time is allocated as long as it doesn’t get in the way of designing. Chip companies… Read More

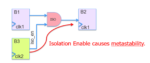

Clock domain crossing (CDC) analysis is unavoidable in any modern SoC design and is challenging enough to verify in its own right. CDC plus low power management adds more excitement to your verification task. I wrote on this topic for another solution provider last year. This time I want to intro an interesting twist on the problem,… Read More

RISC-V has been trending ever since it landed on SemiWiki in 2016. Even more so now that Arm is in flux with the Nvidia acquisition. Verification is a fast growing EDA challenge with the number of verification engineers steadily outpacing design, so this webinar is a best case scenario for SemiWiki traffic, absolutely.

Two things… Read More

Veriest is headquartered in Israel with engineering sites in Serbia & Hungary. The team has accumulated a wealth of experience through involvement in projects in the forefront of semiconductor technology.

Veriest maintains unrivaled quality standards in terms of both service and knowledge. With the ability to take on … Read More

A SoC Design Flow With IP-XACTby Ranjit Adhikary on 07-27-2020 at 10:00 amCategories: EDA, Magillem

Taping out a SoC is never easy. The physical dimensions of the chip often belie the work which has been done to get to the tapeout stage. And it is still not a done deal as the hardware and software development teams await the arrival of the test chip from the foundry to complete the post silicon bring-up and validation. The pressure on… Read More

A paper was published last month on the Acuerdo Consultancy Services website authored by Joe Convey of Acuerdo and Bryan Dickman of Valytic Consulting. Joe and Bryan spent combined decades in the Semi and EDA World which means they have a great understanding of hardware bugs first hand, absolutely.

Here is a quick summary… Read More

Mutation testing is an intriguing idea, but is it useful? Paul Cunningham (GM of Verification at Cadence), Jim Hogan and I continue our series on novel research ideas, here looking at a paper examining the pros and cons of this topic. Feel free to comment if you agree or disagree.

The Innovation

This month’s pick is Which Software … Read More

The irony around this topic in the middle of the coronavirus scare – when more of us are working remotely through the cloud – is not lost on me. Nevertheless, ingrained beliefs move slowly so it’s still worth shedding further light. There is a tribal wisdom among chip designers that what we do demands much higher security than any other… Read More

Non-volatile memory (NVM) is finding new roles in datacenters, not currently so much in “cold storage” as a replacement for hard disk drives, but definitely in “warm storage”. Warm storage applications target an increasing number of functions requiring access to databases with much lower latency than is possible through paths… Read More

I’ve been following the evolution of the verification space for a very long time including several stints consulting to formal verification companies. It has always been interesting to me to see how so many diverse verification techniques emerge and been used, but without much unification of the approaches. With the emergence… Read More