Two weeks ago I blogged about analog verification and it started a discussion with 16 comments, so l’ve found that our readers have an interest in this topic. For decades now the Digital IC design community has used and benefited from regression testing as a way to measure both design quality and progress, ensuring that first… Read More

Tag: verification

CEO Interview: Jens Andersen of Invarian

Invarian is an interesting EDA company that sees a niche market opening in the physical verification space. There are a number of converging factors driving this opportunity. Electromigration and voltage-drop for full-chip analysis demands SPICE level accuracy with fast runtimes. Invarian solves that problem with macro … Read More

Wireless Algorithm Validation from System to RTL to Test

This year’s #50DAC will be chock-full of technical content because that is what attracts the masses of semiconductor professionals, like moths to a flame, or like me to a Fry’s Electronics store. Interesting note, I went to high school with Randy Fry. His Dad started the Fry’s supermarket chain which he sold… Read More

Properly Handing Of Clock Tree Synthesis Specifications

Given today’s design requirements with respect to low power, there is increasing focus on the contribution to total power made by a design’s clock trees. The design decisions made by the front-end team to achieve high performance without wasting power must be conveyed to back-end team. This hand-off must be accurate… Read More

Happy Birthday to Synopsys VIP

I met Mike Sanie around DVCon time and planned to write a blog about the one year anniversary of Synopsys Discovery VIP which was announced during Aart’s keynote at DVCon in 2012. Eric covered it for SemiWiki here. But Synopsys had other stuff they wanted me to blog about and so it is a couple of months late. The 14th month anniversary… Read More

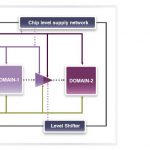

Intelligent tools for complex low power verification

The burgeoning need of high density of electronic content on a single chip, thereby necessitating critical PPA (Power, Performance, Area) optimization, has pushed the technology node below 0.1 micron where static power becomes equally relevant as dynamic power. Moreover, multiple power rails run through the circuit at different… Read More

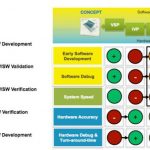

Virtual Platforms, Acceleration, Emulation, FPGA Prototypes, Chips

At CDNLive today Frank Schirrmeister presented a nice overview of Cadence’s verification capabilities. The problem with verification is that you can’t have everything you want. What you really want is very fast runtimes, very accurate fidelity to the hardware and everything available very early in the design … Read More

Verification the Mentor Way

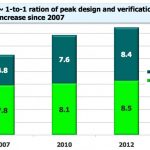

During DVCon I met with Steve Bailey to get an update on Mentor’s verification. They were also announcing some new capabilities. I also attended Wally Rhines keynote (primarily about verification of course, since this was DVCon; I blogged about that here) and the Mentor lunch (it was pretty much Mentor all day for me) on the… Read More

Mentor Shines at DVCon

Mentor Graphics will be all over DVCon next week (February 25-28) at the DoubleTree hotel in San Jose.

In addition to attending all the panels, tutorials, posters, and the keynote, you can visit Mentor in booth 901 on the exhibit floor.

Here’s the lineup of Mentor-related events:… Read More

Jasper User Group Keynotes

I attended the Jasper User Group this week, at least the keynotes, the first by Kathryn Kranen the CEO of Jasper and the second by Bob Bentley of Intel.

Kathryn went over some history, going back to when the company was started (under the name Tempus Fugit) back in August 2002 with a single product for protocol verification. Now, since… Read More