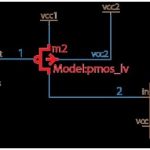

With multiple functionalities added into a single chip, be it a SoC or an ASIC, maintaining low power consumption has become critical for any design. Various techniques at the technology as well as design level are employed to accomplish the low power target. These include thinner oxides in transistors, different sections of … Read More

Tag: verification

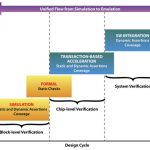

Assertions verifying blocks to systems at Broadcom

Speaking from experience, it is very difficult to get an OEM customer to talk about how they actually use standards and vendor products. A new white paper co-authored by Broadcom lends insight into how a variety of technologies combine in a flow from IP block simulation verification with assertions to complete SoC emulation with… Read More

Cadence’s System-to-Silicon Verification Summit

At this year’s DAC, I spoke with several friends at Cadence. I got the distinct impression that something at Cadence had changed. There was a sense of pride and accomplishment that it seems to me had drifted away over the years. Now employees were speaking with true conviction about the accomplishments of the product development… Read More

Cadence Introduces Palladium XP II

Well, despite all the arguments in the blogosphere about what process node palladium’s silicon is, and whether the design team is competent, and why it reports into sales…Cadence has announced their latest big revision of Palladium. Someone seems to be able to get things done. Of course it is bigger and faster and … Read More

Debugging Verification Constraints

In his DAC keynote last year (2012) Mike Mueller of ARM compared how much CPU was required to verify the first ARM versus one of the latest ARM Cortex CPUs. Of course the newer CPU is hundreds of times larger than the first ARM but the amount of verification required was millions of times as much, requiring ARM to construct their own datacenter… Read More

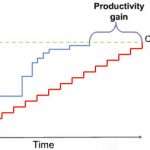

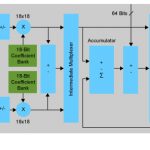

The fixed and the finite: QoR in FPGAs

There is an intriguingly amorphous term in FPGA design circles lately: Quality of Results, or QoR. Fitting a design in an FPGA is just the start – is a design optimal in real estate, throughput, power consumption, and IP reuse? Paradoxically, as FPGAs get bigger and take on bigger signal processing problems, QoR has become a larger… Read More

Missed #50DAC? See Aldec Verification Sessions Online

Aldec, Inc. is an industry-leading Electronic Design Automation (EDA) company delivering innovative design creation, simulation and verification solutions to assist in the development of complex FPGA, ASIC, SoC and embedded system designs. With an active user community of over 35,000, 50+ global partners, offices worldwide… Read More

So, where are all the EMBEDDED guys?

Roaming the aisles at #50DAC the past week left me with one unmistakable impression: there were two shows going on at the same time. Oh, we were all packed into one space together at the Austin Convention Center and neighboring hotels. But we weren’t quite all speaking the same language – yet.… Read More

Hardware Assisted Verification

On the Tuesday of DAC I moderated a panel session on Hardware Assisted Verification in 10 Years: More Need, More Speed. Although this topic obviously could include FPGA-based prototyping, in fact we spent pretty much the whole time talking about emulation. Gary Smith, on Sunday night, actually set up things by pointing out that… Read More

Jasper’s DAC Program

Jasper’s booth is 2346 where you can see demos of the JasperGold Apps and attend seminars on the experiences of ST and Broadcom, and others:

- The Broadcom presentation on making formal an integral part of chip design is Tuesday at 10am.

- The ST presentation on adapting formal methods in ARM subsystems is Monday at 1.30pm and