Learning is a never-ending process for design and verification engineers, so outside of reading SemiWiki you likely want to attend at least a few events per year to keep updated, learn something new, attend a workshop, or even present something that has made your IC project work much better than before. Sure, DAC is always a great… Read More

Tag: uvm

PSS and Reuse: Great Solution But Not Hands-Free

If you’re new to PSS you could be forgiven for thinking that it automagically makes stimulus reusable, vertically from IPs to systems, horizontally between derivatives and between hardware-based and software-based testing. From a big-picture point of view these are certainly all potential benefits of PSS.

What PSS does provide… Read More

CEO Interview: Adnan Hamid of Breker Systems

Breker Verification Systems solves challenges across the functional verification process for large, complex semiconductors. This includes streamlining UVM-based testbenches for IP verification, synchronizing software and hardware tests for large system-on-chips (SoCs), and simplifying test sets for hardware emulation… Read More

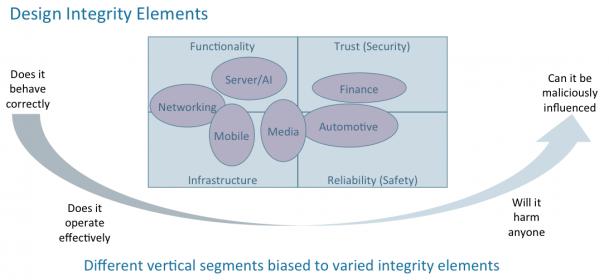

Design Integrity Investment Thesis Part 2

It is important when talking about a market to first establish the need and potential growth, then determine how the market is being served. This requires examining product features and services offered. … Read More

Portable Stimulus enables new design and verification methodologies

My usual practice when investing is to look at startup companies and try to understand if the market they are looking to serve has a significant opportunity for a new and disruptive technology. This piece compiles the ideas that I used to form an investment thesis in Portable Stimulus. Once collected, I often share ideas to get feedback.… Read More

CEO Interview: Cristian Amitroaie of AMIQ EDA

AMIQ EDA has caught my attention over the last few months. My first impression was that this was just another small IDE company trying to compete with established and bundled IDEs from the big 3, a seemingly insurmountable barrier. This view was challenged by an impressive list of testimonials, not just from the little guys but also… Read More

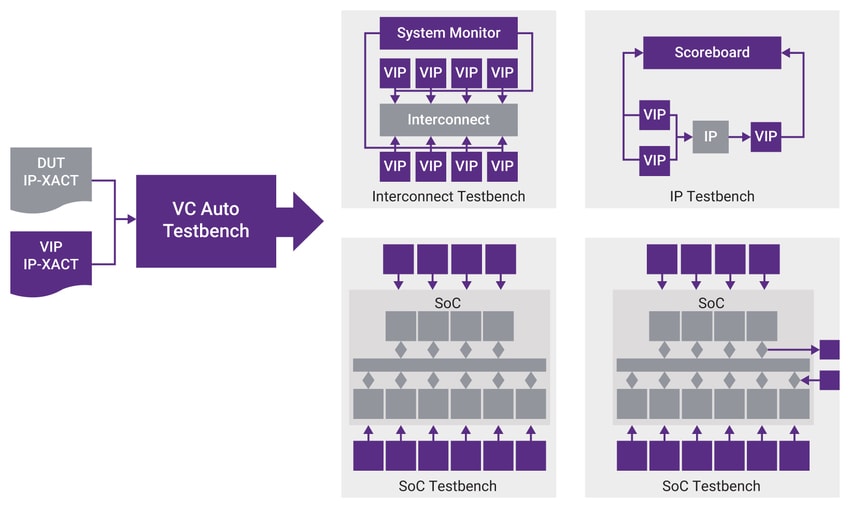

Webinar: Fast-track SoC Verification – Reduce time-to-first-test with Synopsys VC AutoTestbench

There seems to be a general sense that we have the foundations for block/IP verification more or less under control, thanks to UVM standardizing infrastructure for directed and constrained-random testing, along with class libraries providing building blocks to simplify verification reuse, build sequence tests, verify register… Read More

Case study illustrates 171x speed up using SCE-MI

As SoC design size and complexity increases, simulation alone falls farther and farther behind, even with massive cloud farms of compute resources. Hardware acceleration of simulation is becoming a must-have for many teams, but means more than just providing emulation… Read More

Five Things To See at DVCon India 2016

DVCon is an annual Design and Verification Conference that started out in Silicon Valley, then expanded by adding India as a new location. Our semiconductor design and verification world is global in stature, so if you’re living in the region then consider registering for this event held Thursday and Friday, September … Read More

A New Player in the Functional Verification Space

Israel has a strong pedigree in functional verification. Among others, Verisity (an early contributor to class-based testbench design and constrained random testing) started in Israel and RocketTick (hardware-based simulation acceleration), acquired more recently by Cadence, is based in Israel. So when I hear about an … Read More