Recently we have been swamped by news of Artificial Intelligence applications in hardware and software by the increased adoption of Machine Learning (ML) and the shift of electronic industry towards IoT and automobiles. While plenty of discussions have covered the progress of embedded intelligence in product roll-outs, an… Read More

Tag: tsmc

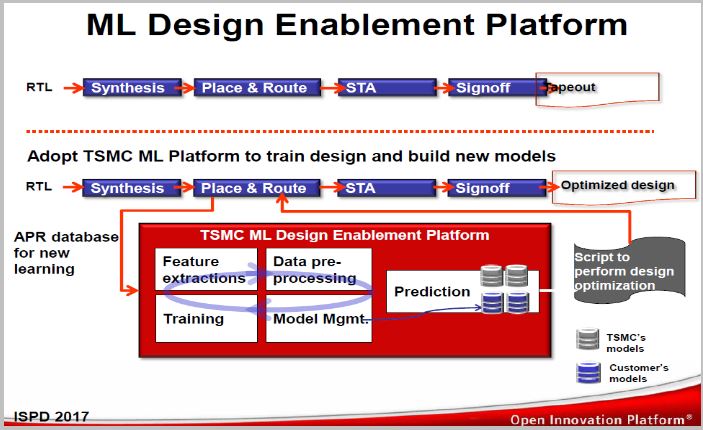

Deep Learning and Cloud Computing Make 7nm Real

The challenges of 7nm are well documented. Lithography artifacts create exploding design rule complexity, mask costs and cycle time. Noise and crosstalk get harder to deal with, as does timing closure. The types of applications that demand 7nm performance will often introduce HBM memory stacks and 2.5D packaging, and that creates… Read More

Choosing the lesser of 2 evils EUV vs Multi Patterning!

For Halloween this week we thought it would be appropriate to talk about things that strike fear into the hearts of semiconductor makers and process engineers toiling away in fabs. Do I want to do multi-patterning with the huge increase in complexity, number of steps, masks and tools or do I want to do EUV with unproven tools, unproven… Read More

Arm TechCon Preview with the Foundries!

This week Dr. Eric Esteve, Dr. Bernard Murphy, and I will be blogging live from Arm TechCon. It really looks like it will be a great conference so you should see some interesting blogs in the coming days. One of the topics I am interested in this year is foundation IP and I will tell you why.

During the fabless transformation of the semiconductor… Read More

TSMC: Semiconductors in the next ten years!

The TSMC 30th Anniversary Forum just ended so I will share a few notes before the rest of the media chimes in. The forum was live streamed on tsmc.com, hopefully it will be available for replay. The ballroom at the Grand Hyatt in Taipei was filled with cameras, semiconductor executives, and security personnel.

The… Read More

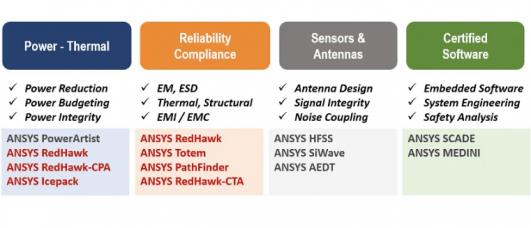

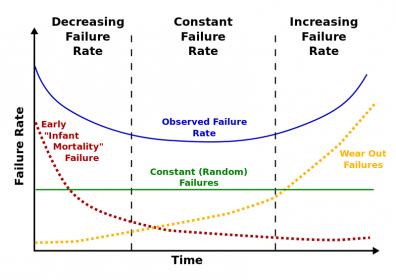

Reliability Signoff for FinFET Designs

Ansys recently hosted a webinar on reliability signoff for FinFET-based designs, spanning thermal, EM, ESD, EMC and aging effects. I doubt you’re going to easily find a more comprehensive coverage of reliability impact and analysis solutions. If you care about reliability in FinFET designs, you might want to check out this webinar.… Read More

TechCon: See ANSYS and TSMC co-present

ANSYS and TSMC will be co-presenting at ARM TechCon on Multiphysics Reliability Signoff for Next Generation Automotive Electronics Systems. The event is on Thursday October 26th, 10:30am-11:20am in Grand Ballroom B.

You can get a free Expo pass which will give you access to this event HERE and see the session page for the event … Read More

TSMC Teamwork Translates to Technical Triumph

Most people think that designing successful high speed analog circuits requires a mixture of magic, skill and lots of hard work. While this might be true, in reality it also requires a large dose of collaboration among each of the members of the design, tool and fabrication panoply. This point was recently made abundantly clear … Read More

This is a Different GLOBALFOUNDRIES!

Having followed GF since its inception, I agree with CTO Gary Patton, what we are seeing today truly is a different GLOBALFOUNDRIES! Our first GF blog was published on 9/13/2009 and we have done a total of 173 GF related blogs that have collected more than 1.5M views thus far. 72 of those blogs were written by me so I have followed this… Read More

What does the Lattice rejection mean for chip M&A?

Although the rejection of the Lattice deal was expected, it none the less has an impact on a number of dynamics in the chip industry and further M&A and consolidation. Freezing out China removes a “catalyst” in the market which help bid up values and add fear to both potential targets or those left out. Cross border… Read More