Digital verification engineers have developed robust, thorough metrics for evaluating design coverage. Numerous tools are available to evaluate testbenches against RTL model descriptions — e.g., confirming that simulation regressions exhaustively exercise signal toggles, RTL statement lines, individual statement… Read More

Tag: tom dillinger

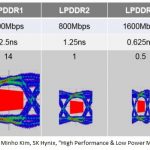

PCB Design Requires Both Speed and Accuracy of SI/PI Analysis

The prevailing industry trends are clear: (1) PCB and die package designs are becoming more complex, across both mobile and high-performance applications; (2) communication interface performance between chips (and their related protocols) is increasingly demanding to verify; (3) signal integrity and power integrity issues… Read More

Improvements in SRAM Yield Variation Analysis

The design of an SRAM array requires focus on the key characteristics of readability, writeability, and read stability. As technology scaling has enabled the integration of large (cache) arrays on die, the sheer number of bitcells has necessitated a verification methodology that focuses on “statistical high-sigma” variation… Read More

Key Takeaways from the TSMC Technology Symposium Part 2

In Part 1, we reviewed four of the highlights of the recent TSMC Technology Symposium in San Jose. This article details the “Final Four” key takeaways from the TSMC presentations, and includes a few comments about the advanced technology research that TSMC is conducting.… Read More

Key Takeaways from the TSMC Technology Symposium Part 1

TSMC recently held their annual Technology Symposium in San Jose, a full-day event with a detailed review of their semiconductor process and packaging technology roadmap, and (risk and high-volume manufacturing) production schedules.… Read More

DDR4 is a complex interface to verify — assistance needed!

The design of parallel interfaces is supposed to be (comparatively) easy — e.g., follow a few printed circuit board routing guidelines; pay attention to data/clock/strobe signal lengths and shielding; ensure good current return paths (avoid discontinuities); match the terminating resistances to the PCB trace impedance;… Read More

Top Ten Insights on the EDA and Semiconductor Industry

I recently had the opportunity to chat with Anirudh Devgan, senior vice president and general manager at Cadence, who leads the Digital and Signoff Group. We discussed recent product development initiatives at Cadence, and talked about future EDA and semiconductor market opportunities. His insights and comments were keen … Read More

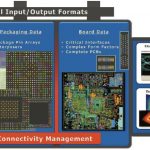

Pathfinding to an Optimal Chip/Package/Board Implementation

A new term has entered the vernacular of electronic design engineering — pathfinding. The complexity of the functionality to be integrated and the myriad of chip, package, and board technologies available make the implementation decision a daunting task. Pathfinding refers to the method by which the design space of technology… Read More

Expanding 3D EM Simulation Access to All

James Clerk Maxwell’s eponymous equations are the basis for simulating electromagnetic wave propagation. In school, EE majors tended to fall into two camps: (a) those that thoroughly enjoyed their fields and waves classes, who liked doing surface integrals, and who were adept at demonstrating the “right hand rule”, and (b) … Read More

HSPICE – 35 and looking good!

A maturetool. A legacytool. A tool that’s a little long in the tooth. We have all used these terms to refer to an EDA product that has not been able to keep up with technical challenges of model complexity, performance, or new features required by current SoC and system design requirements.… Read More