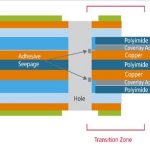

Printed circuit boards that incorporate a combination of traditional PCB technology with flexible substrates, aka rigid-flex designs, have enabled an increasing variety of product designs, that leverage the unique physical form factor and lightweight options that rigid-flex technology offers. Yet, this technology requires… Read More

Tag: tom dillinger

ESL Architectural Power Estimation Support from TSMC — yes, TSMC

Electronic system level (ESL) modeling for system architecture exploration is rapidly gaining momentum. The simulation performance requirements for hardware/software co-design are demanding — an abstract model for SoC IP cores is required. Typically, soft IP will include a number of model configuration parameters.… Read More

The Package Assembly Design Kit (PADK)… the start of something big

Integrated wafer-level fanout (WLFO) packaging technology is emerging as a foundation for multi-die solutions. Mobile product applications require focus on both aggressive chip-to-chip interface performance, as well as the final package volume. Traditional multi-chip packages using PCB laminate substrates do not readily… Read More

Is the U.S. ready to adopt a new financial model to support microelectronics?

Amidst all the active news about new process introductions at 16/14/10/7nm and the status of next-generation lithography development, there was a recent press release that could have as large an impact upon the microelectronics industry in the United States. A groundbreaking ceremony was recently held in Marcy, New York for… Read More

Top Ten #53DAC Highlights

Here is a very subjective list of the Top 10 logistical and technical highlights from DAC’53.

(10) With DAC attendance down from its peak days, the Austin Convention Center served as an excellent venue. There was good participation from companies with design centers in the “Silicon Hills”. And, I saw colleagues from Silicon Valley,… Read More

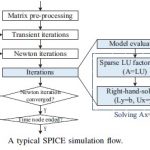

The Emerging Importance of Parallel SPICE

SPICE simulation is the workhorse tool for custom circuit timing validation and electrical analysis. As the complexity of blocks and macros has increased in advanced process nodes — especially with post-layout extraction parasitic elements annotated to the circuit netlist — the model size and simulation throughput… Read More

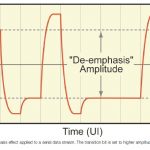

Channel Operating Margin (COM) — A Standard for SI Analysis

There’s an old adage, attributed to renowned computer scientist Andrew Tannenbaum, one that perhaps only engineers find amusing: “The nice thing about standards is that you have so many to choose from.” Nevertheless, IEEE standards arise from customer requirements in the electronics industry. Many relate… Read More

TSMC and Solido on Variation-Aware Design of Memory and Standard Cell at Advanced Process Nodes

Being that TSMC and Solido are founding members of SemiWiki, you should be able find out everything you ever wanted to know on their respective landing pages. If not, just ask a question in the SemiWiki forum and I can assure you it will be answered in great detail. And here are some other interesting 2015 factoids from Solido:… Read More

A Better Way for Analog Designers to Perform Variation Analysis

The impact of process variation at advanced nodes is increasing — no surprise there. In recent years, the principal design emphasis to better reflect this variation has been the adoption of two new methodologies: (1) advanced on-chip variation (AOCV, as well as POCV/LVF) for digital static timing analysis, and (2) advanced… Read More

Custom Layout Productivity Gets a Boost

In the 1970’s, when Moore’s Law was still in its infancy, Bill Lattin from Intel published a landmark paper [1]. In it he identified the need for new design tools and methods to improve layout productivity, which he defined as the drawn and verified number of transistors per day per layout designer. He said existing … Read More