Machine learning-based applications have become prevalent across consumer, medical, and automotive markets. Still, the underlying architecture(s) and implementations are evolving rapidly, to best fit the throughput, latency, and power efficiency requirements of an ever increasing application space. Although ML is … Read More

Tag: tom dillinger

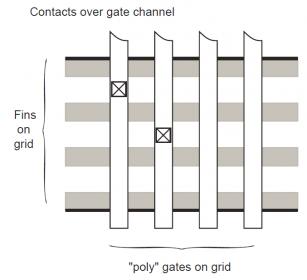

Top 10 Highlights from the Samsung Foundry Forum

Samsung Foundry recently held their annual technology forum in Santa Clara CA. The forum consisted of: presentations on advanced and mainstream process technology roadmaps; the IP readiness for those technology nodes; a review of several unique package offerings; and, an informal panel discussion with IP designers and EDA… Read More

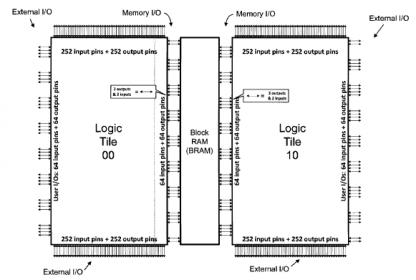

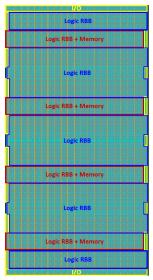

Block RAM integration for an Embedded FPGA

The upcoming Design Automation Conference in San Francisco includes a very interesting session –“Has the Time for Embedded FPGA Come at Last?” Periodically, I’ve been having coffee with the team at Flex Logix, to get their perspective on this very question – specifically, to learn about the key features that customers are seeking… Read More

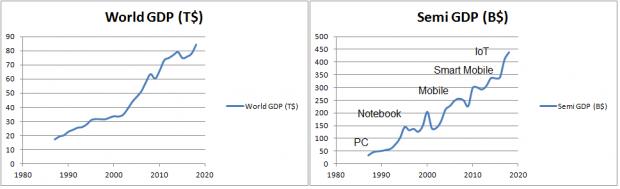

Top 10 Highlights of the TSMC 2018 Technology Symposium

Here are the Top 10 highlights from the recent TSMC 2018 Technology Symposium, held in Santa Clara CA. A couple of years ago, TSMC acknowledged the unique requirements of 4 different market segments, which has since guided their process development strategy — Mobile, High-Performance Computing (HPC), Automotive, and… Read More

Hard IP for an embedded FPGA

As Moore’s Law enables increased integration, the diversity of functionality in SoC designs has grown. Design teams are seeking to utilize outside technical expertise in key functional areas, and to accelerate their productivity by re-using existing designs that others have developed. The Intellectual Property (IP) industry… Read More

Configurability for Embedded FPGA Hard IP

IP providers need to evaluate several complex engineering problems when addressing customer requirements – perhaps the most intricate challenge is the degree of IP configurabilityavailable to satisfy unique customer applications. … Read More

An OSAT Reference Flow for Complex System-in-Package Design

With each new silicon process node, the complexity of SoC design rules and physical verification requirements increases significantly. The foundry and an EDA vendor collaborate to provide a “reference flow” – a set of EDA tools and process design kit (PDK) data that have been qualified for the new node. SoC design methodology … Read More

IPC-2581: The Standard for PCB Data Exchange

The motivations to establish an industry standard data format are varied:

[LIST=1]

- solidify a “de facto” standard, transitioning its evolution and support from a single company to an industry consortium;

- aggregate disparate sources of design and manufacturing data into a single representation, with documented semantics;

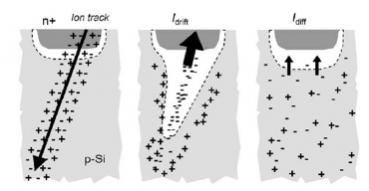

Adapting an embedded FPGA for Aerospace Applications

The IC industry is commonly divided into different market segments – consumer, mobile, industrial, commercial, medical, automotive, and aerospace. A key differentiation among these segments is the characterization and reliability qualification strategy for the fabrication process and design circuitry. For each segment,… Read More

Scoreboard and Issues Management Tools for PCB Projects

The complexity of an SoC design necessitates that the project managers have accurate visibility into the overall design status, spanning the entire range of tasks – from functional simulation error triage, to physical layout verification errors, to electrical analysis results. Flow scripts used by SoC teams parse the log file… Read More