The Universal Verification Methodology (UVM) is a popular way to help verify SystemVerilog designs, and it includes a configuration system that unfortunately has some speed and usage issues. Rich Edelman from Siemens EDA wrote a detailed 20-page paper on the topic of how to avoid these issues, and I’ve gone through it to… Read More

Tag: testbench

Register Automation for a DDR PHY Design

Several months ago, I interviewed Anupam Bakshi, the CEO and founder of Agnisys. I wanted to learn more about the company, so I listened to a webinar that covered their latest products and how they fit together into an automated flow. I posted my thoughts and then I became curious about their customers, so I asked Anupam to arrange … Read More

How Good is Your Testbench?

I’ve always been intrigued by Synopsys’ Certitude technology. It’s a novel approach to the eternal problem of how to get better coverage in verification. For a design of any reasonable complexity, the state-space you would have to cover to exhaustively consider all possible behaviors is vastly larger than you could ever possibly… Read More

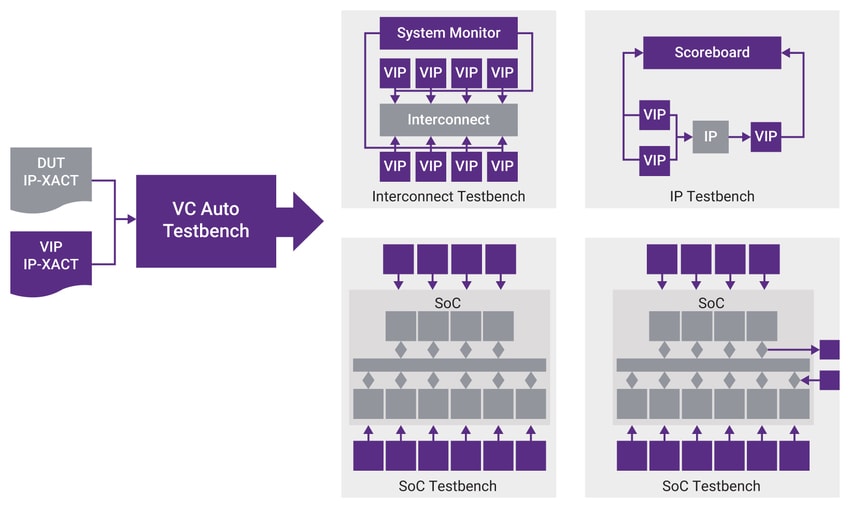

Webinar: Fast-track SoC Verification – Reduce time-to-first-test with Synopsys VC AutoTestbench

There seems to be a general sense that we have the foundations for block/IP verification more or less under control, thanks to UVM standardizing infrastructure for directed and constrained-random testing, along with class libraries providing building blocks to simplify verification reuse, build sequence tests, verify register… Read More

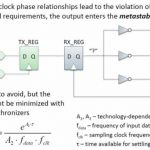

Up front phases improve CDC analysis

Many tools find clock domain crossings (CDCs) in FPGA designs. Some don’t find the right ones since they don’t comprehend things like in-house synchronizer constructs. Some find too many based on misunderstanding intent, inaccurate constraints, and other factors that lead to noise.… Read More

Market Trends Motivate a Shift-Left in Functional Verification

Today, in the context of functional verification, industry trends are based on the needs of prominent vertical markets. There is some overlap in what these markets need, but there are some use models that are very specific to each market.

We assert this because we have a lot of customers asking about emulation solutions not from … Read More

Pseudo random generator tutorial in VHDL (Part 3/3)

On the first two chapters of this Tutorial we started with a simple LFSR module and added a test bench. Then, on chapters three and four we upgraded our module with some features and learned to export the test bench data to files.

… Read More

Pseudo random generator tutorial in VHDL (Part 2/3)

In the first part of this tutorialwe started with a simple implementation of an LFSR block (Chapter 1) and its test bench (Chapter 2). Let’s make our code look a bit more professional.

… Read More

Pseudo random generator tutorial in VHDL (Part 1/3)

In this tutorial we will see how to design a VHDL block. We will start with a very simple block and we will gradually add features to it. We will also simulate it and test its output with Matlab. Over the process we will see:

… Read More

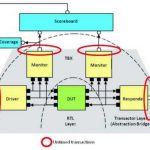

Striving for one code base in accelerated testbenches

Teams buy HDL simulation for best bang for the buck. Teams buy hardware emulation for the speed. We’ve talked previously about SCE-MI transactors as a standardized vehicle to connect the two approaches to get the benefits of both in an accelerated testbench – what else should be accounted for?… Read More